#### 8 - Bit Micro-controller

64KB ISP flash & 1KB RAM embedded

#### **Product List**

SM5964C25, 25 MHz 64KB internal flash MCU SM5964C40, 40 MHz 64KB internal flash MCU

# Description

The SM5964 series product is an 8 - bit single chip microcontroller with 64KB flash & 1K byte RAM embedded. It has In-System Programming (ISP) function and is a derivative of the 8052 microcontroller family. It has 5-channel SPWM build-in. User can access on-chip expanded RAM with easier and faster way by its 'bank mapping direct addressing mode' scheme. With its hardware features and powerful instruction set, it's straight forward to make it a versatile and cost effective controller for those applications which demand up to 32 I/O pins for PDIP package or up to 36 I/O pins for PLCC/QFP package, or applications which need up to 64K byte flash memory either for program or for data or mixed.

To program the on-chip flash memory, a commercial writer is available to do it in parallel programming method. The on-chip flash memory can be programmed in either parallel or serial interface with its ISP feature.

# Ordering Information

yywwv SM5964ihhk

yy: year, ww:week

v: version identifier { , A, B, ...}

i: process identifier

hh: working clock in MHz {25, 40} k: package type postfix {as below table}

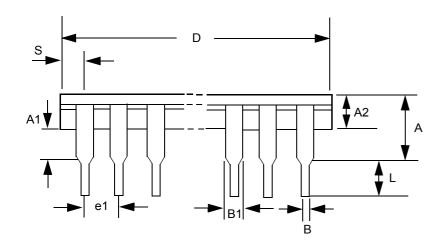

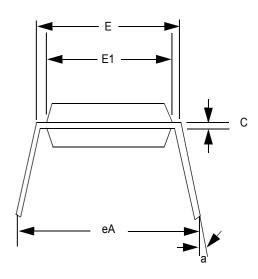

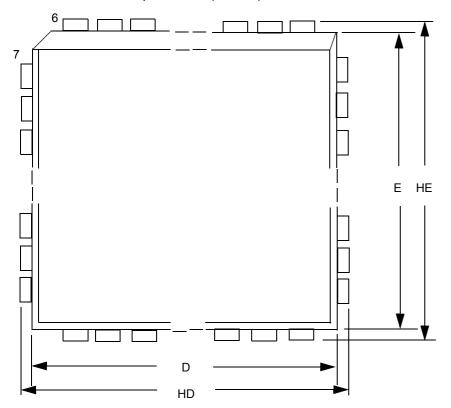

| Postfix | Package  | Pin/Pad<br>Configuration | Dimension |

|---------|----------|--------------------------|-----------|

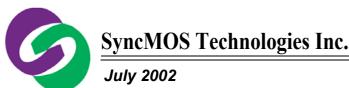

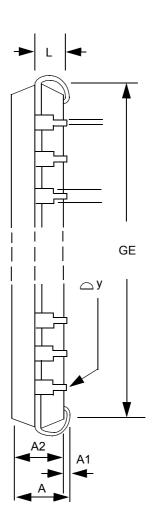

| Р       | 40L PDIP | page 2                   | page 24   |

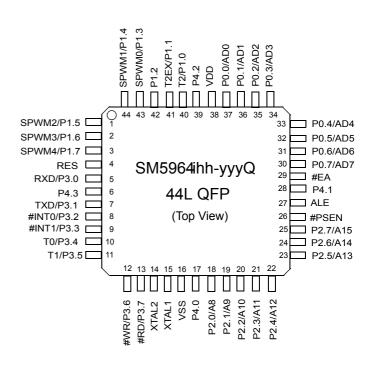

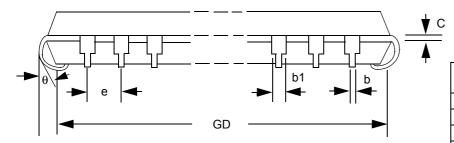

| J       | 44L PLCC | page 2                   | page 25   |

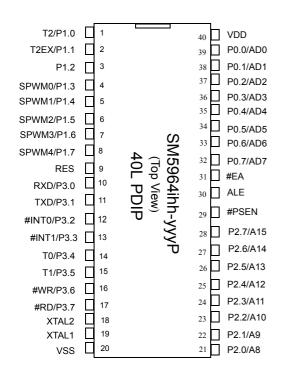

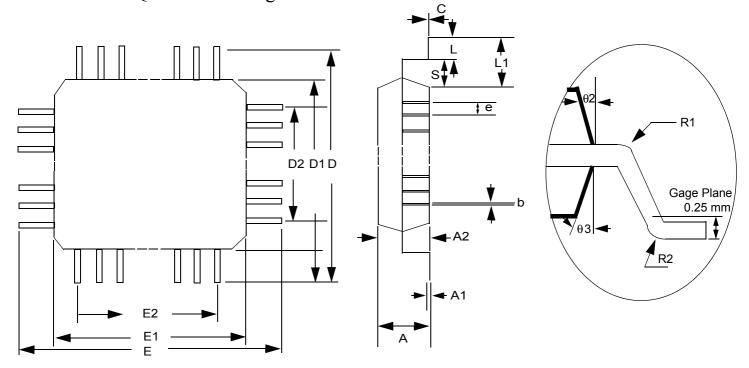

| Q       | 44L QFP  | page 2                   | page 26   |

#### Features

- Working voltage: 4.5V through 5.5V

- General 8052 family compatible

- 12 clocks per machine cycle

- 64K byte on chip flash memory with In-System

- Programming (ISP) capability

- 1024 byte on chip data RAM

- Three 16 bit Timers/Counters

- One Watch Dog Timer

- Four 8-bit I/O ports for PDIP package

- Four 8-bit I/O ports + one 4-bit I/O ports for PLCC or QFP package

- Full duplex serial channel

- Bit operation instruction

- Page free jumps

- 8-bit Unsigned Division

- 8-bit Unsigned Multiply

- BCD arithmetic

- **Direct Addressing**

- Indirect Addressing

- Nested Interrupt

- Two priority level interrupt

- A serial I/O port

- Power save modes:

- Idle mode and Power down mode

- Code protection function

- Low EMI (inhibit ALE)

- Reset with address \$0000 blank initiate ISP service program

- ISP service program space configurable in N\*512byte (N=0 to 8) size

- Bank mapping direct addressing mode for access on-chip

- Five channel Specific PWM (SPWM) build-in with P1.3 ~ P1.7

Taiwan 4F, No. 1 Creation Road 1, Science-based Industrial Park, Hsinchu, Taiwan 30077

TEL: 886-3-578-3344 886-3-579-2988 FAX: 886-3-579-2960 886-3-578-0493

Website: http://www.syncmos.com.tw

# **Pin Configurations**

July 2002

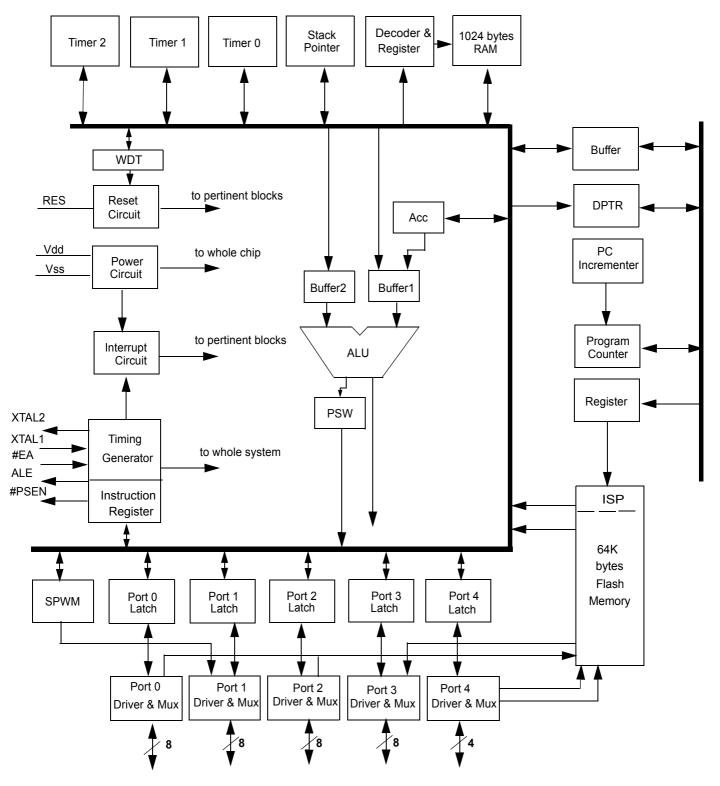

# **Block Diagram**

3/28

# Pin Descriptions

| 40L  | 44L | 44L  |            |            |     |                                                         |

|------|-----|------|------------|------------|-----|---------------------------------------------------------|

| PDIP |     | PLCC | Symbol     | Active     | I/O | Names                                                   |

| Pin# | -   |      |            | 7 10 11 10 |     | 1                                                       |

| 1    | 40  | 2    | T2/P1.0    |            | i/o | timer 2 clock out & bit 0 of port 1                     |

| 2    | 41  | 3    | T2EX/P1.1  |            | i/o | timer 2 control & bit 1 of port 1                       |

| 3    | 42  | 4    | P1.2       |            | i/o | bit 2 of port 1                                         |

| 4    | 43  | 5    | SPWM0/P1.3 |            | i/o | SPWM Channel 0, bit 3 of port 1                         |

| 5    | 44  | 6    | SPWM1/P1.4 |            | i/o | SPWM Channel 1, bit 4 of port 1                         |

| 6    | 1   | 7    | SPWM2/P1.5 |            | i/o | SPWM Channel 2, bit 5 of port 1                         |

| 7    | 2   | 8    | SPWM3/P1.6 |            | i/o | SPWM Channel 3, bit 6 of port 1                         |

| 8    | 3   | 9    | SPWM4/P1.7 |            | i/o | SPWM Channel 4, bit 7 of port 1                         |

| 9    | 4   | 10   | RES        | Н          | i   | Reset                                                   |

| 10   | 5   | 11   | RXD/P3.0   |            | i/o | Receive data & bit 0 of port 3                          |

| 11   | 7   | 13   | TXD/P3.1   |            | i/o | Transmit data & bit 1 of port 3                         |

| 12   | 8   |      | #INT0/P3.2 | L/ -       | i/o | low true interrupt 0 & bit 2 of port 3                  |

| 13   | 9   |      | #INT1/P3.3 | L/ -       | i/o | low true interrupt 1 & bit 3 of port 3                  |

| 14   | 10  |      | T0/P3.4    |            | i/o | Timer 0 & bit 4 of port 3                               |

| 15   | 11  |      | T1/P3.5    |            | i/o | Timer 1 & bit 5 of port 3                               |

| 16   | 12  |      | #WR/P3.6   | L/ -       | i/o | ext. memory write & bit 6 of port 3                     |

| 17   | 13  | 19   | #RD/P3.7   | L/ -       | i/o | ext. memory read & bit 7 of port 3                      |

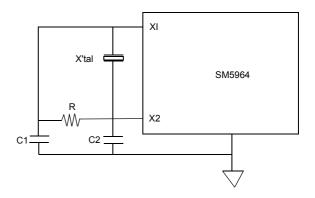

| 18   | 14  |      | XTAL2      |            | 0   | Crystal out                                             |

| 19   | 15  |      | XTAL1      |            | i   | Crystal in                                              |

| 20   | 16  | 22   | VSS        |            |     | Sink Voltage, Ground                                    |

| 21   | 18  |      | P2.0/A8    |            | i/o | bit 0 of port 2 & bit 8 of external memory address      |

| 22   | 19  |      | P2. 1/A9   |            | i/o | bit 1 of port 2 & bit 9 of external memory address      |

| 23   | 20  | 26   | P2.2/A10   |            | i/o | bit 2 of port 2 & bit 10 of external memory address     |

| 24   | 21  |      | P2.3/A11   |            | i/o | bit 3 of port 2 & bit 11 of external memory address     |

| 25   | 22  |      | P2.4/A12   |            | i/o | bit 4 of port 2 & bit 12 of external memory address     |

| 26   | 23  |      | P2.5/A13   |            | i/o | bit 5 of port 2 & bit 13 of external memory address     |

| 27   | 24  |      | P2.6/A14   |            | i/o | bit 6 of port 2 & bit 14 of external memory address     |

| 28   | 25  |      | P2.7/A15   |            | i/o | bit 7 of port 2 & bit 15 of external memory address     |

| 29   | 26  |      | #PSEN      | L          | 0   | program storage enable                                  |

| 30   | 27  |      | ALE        | -          | 0   | address latch enable                                    |

| 31   | 29  |      | #EA        | L          | i   | external access                                         |

| 32   | 30  |      | P0.7/AD7   |            |     | bit 7 of port 0 & data/address bit 7 of external memory |

| 33   | 31  |      | P0.6/AD6   |            |     | bit 6 of port 0 & data/address bit 6 of external memory |

| 34   | 32  |      | P0.5/AD5   |            | i/o | bit 5 of port 0 & data/address bit 5 of external memory |

| 35   | 33  |      | P0.4/AD4   |            | i/o | bit 4 of port 0 & data/address bit 4 of external memory |

| 36   | 34  |      | P0.3/AD3   |            | i/o | bit 3 of port 0 & data/address bit 3 of external memory |

| 37   | 35  |      | P0.2/AD2   |            | i/o | bit 2 of port 0 & data/address bit 2 of external memory |

| 38   | 36  |      | P0.1/AD1   |            | i/o | bit 1 of port 0 & data/address bit 1 of external memory |

| 39   | 37  |      | P0.0/AD0   |            | i/o | bit 0 of port 0 & data/address bit 0 of external memory |

| 40   | 38  | 44   | VDD        |            |     | Drive Voltage                                           |

|      | 17  |      | P4.0       |            |     | bit 0 of Port 4                                         |

|      | 28  |      | P4.1       |            |     | bit 1 of Port 4                                         |

|      | 39  |      | P4.2       |            | i/o | bit 2 of Port 4                                         |

|      | 6   | 12   | P4.3       |            | i/o | bit 3 of Port 4                                         |

4/28

# **Special Function Register (SFR)**

The address \$80 to \$FF can be accessed by direct addressing mode only. Address \$80 to \$FF is SFR area.

The following table list the SFRs which are identical to general 8052 as well as SM5964 Extension SFRs.

| \$F8 |       |       |        |        |        |        |        |        | \$FF |

|------|-------|-------|--------|--------|--------|--------|--------|--------|------|

| \$F0 | В     |       |        |        | ISPFAH | ISPFAL | ISPFD  | ISPC   | \$F7 |

| \$E8 |       |       |        |        |        |        |        |        | \$EF |

| \$E0 | ACC   |       |        |        |        |        |        |        | \$E7 |

| \$D8 | P4    |       |        |        |        |        |        |        | \$DF |

| \$D0 | PSW   |       |        |        |        |        |        |        | \$D7 |

| \$C8 | T2CON | T2MOD | RCAP2L | RCAP2H | TL2    | TH2    |        |        | \$CF |

| \$C0 |       |       |        |        |        |        |        |        | \$C7 |

| \$B8 | IP    |       |        |        |        |        |        | SCONF  | \$BF |

| \$B0 | P3    |       |        |        |        |        |        |        | \$B7 |

| \$A8 | ΙE    |       |        |        | SPWMD4 |        |        |        | \$AF |

| \$A0 | P2    |       |        | SPWMC  | SPWMD0 | SPWMD1 | SPWMD2 | SPWMD3 | \$A7 |

| \$98 | SCON  | SBUF  |        | P1CON  |        |        |        | WDTC   | \$9F |

| \$90 | P1    |       |        |        |        |        |        | WDTKEY | \$97 |

| \$88 | TCON  | TMOD  | TL0    | TL1    | TH0    | TH1    |        |        | \$8F |

| \$80 | P0    | SP    | DPL    | DPH    |        | RCON   | DBANK  | PCON   | \$87 |

Note: The text of SFRs with bold type characters are Extension Special Function Registers for SM5964

| Addr | SFR    | Reset     | 7        | 6        | 5        | 4        | 3        | 2      | 1      | 0      |

|------|--------|-----------|----------|----------|----------|----------|----------|--------|--------|--------|

| 85H  | RCON   | ******00  |          |          |          |          |          |        | RAMS1  | RAMS0  |

| 86H  | DBANK  | 0***0001  | BSE      |          |          |          | BS3      | BS2    | BS1    | BS0    |

| 9BH  | P1CON  | 00000***  | SPWM4E   | SPWM3E   | SPWM2E   | SPWM1E   | SPWM0E   |        |        |        |

| 9FH  | WDTC   | 0*0**000  | WDTE     |          | CLEAR    |          |          | PS2    | PS1    | PS0    |

| АЗН  | SPWMC  | ******00  |          |          |          |          |          |        | FPDIV1 | FPDIV0 |

| A4H  | SPWMD0 | 00H       | SPWMD0.4 | SPWMD0.3 | SPWMD0.2 | SPWMD0.1 | SPWMD0.0 | BRM0.2 | BRM0.1 | BRM0.0 |

| A5H  | SPWMD1 | 00H       | SPWMD1.4 | SPWMD1.3 | SPWMD1.2 | SPWMD1.1 | SPWMD1.0 | BRM1.2 | BRM1.1 | BRM1.0 |

| A6H  | SPWMD2 | 00H       | SPWMD2.4 | SPWMD2.3 | SPWMD2.2 | SPWMD2.1 | SPWMD2.0 | BRM2.2 | BRM2.1 | BRM2.0 |

| A7H  | SPWMD3 | 00H       | SPWMD3.4 | SPWMD3.3 | SPWMD3.2 | SPWMD3.1 | SPWMD3.0 | BRM3.2 | BRM3.1 | BRM3.0 |

| ACH  | SPWMD4 | 00H       | SPWMD4.4 | SPWMD4.3 | SPWMD4.2 | SPWMD4.1 | SPWMD4.0 | BRM4.2 | BRM4.1 | BRM4.0 |

| BFH  | SCONF  | 0****010  | WDR      |          |          |          |          | ISPE   | OME    | ALEI   |

| C9H  | T2MOD  | ******00* | *        | *        | *        | *        | *        | *      | T2OE   | DCEN   |

| D8H  | P4     | ****1111  |          |          |          |          | P4.3     | P4.2   | P4.1   | P4.0   |

| Addr | SFR    | Reset    | 7     | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

|------|--------|----------|-------|------|------|------|------|------|-----|-----|

| F4H  | ISPFAH | 00H      | FA15  | FA14 | FA13 | FA12 | FA11 | FA10 | FA9 | FA8 |

| F5H  | ISPFAL | 00H      | FA7   | FA6  | FA5  | FA4  | FA3  | FA2  | FA1 | FA0 |

| F6H  | ISPFD  | 00H      | FD7   | FD6  | FD5  | FD4  | FD3  | FD2  | FD1 | FD0 |

| F7H  | ISPC   | 0*****00 | START |      |      |      |      |      | F1  | F0  |

# **Extension Function Description**

#### 1. Memory Structure

The SM5964 is the general 8052 hardware core to integrate the ISP function module as a single chip microcontroller. Its memory structure follows general 8052 structure.

#### 1.1 Program Memory

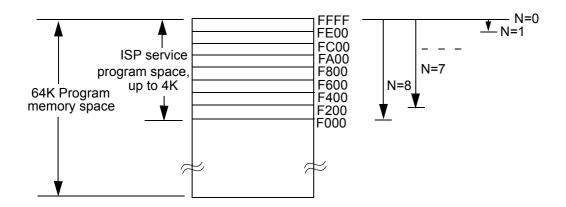

The SM5964 has 64K byte on-chip flash memory which used as general program memory, on which include up to 4K byte specific ISP service program memory space. The address range for the 64K byte is \$0000 to \$FFFF. The address range for the ISP service program is \$F000 to \$FFFF. The ISP service program size can be partitioned as N blocks of 512 byte (N=0 to 8). When N=0 means no ISP service program space available, total 64K byte memory used as program memory. When N=1 means memory address \$FE00 to \$FFFF reserved for ISP service program. When N=2 means memory address \$FC00 to FFFF reserved for ISP service program,...etc. Value N can be set and programmed into SM5964 by writer.

#### 1.2 Data Memory

The SM5964 has 1K bytes on-chip RAM, 256 bytes of it are the same as general 8052 internal memory structure while the expanded 768 bytes on-chip RAM can be accessed by external memory addressing method (by instruction MOVX.) or by bank mapping direct addressing mode.

|          | July 2002                                                      |                                               |    |                                                                                                 |      |

|----------|----------------------------------------------------------------|-----------------------------------------------|----|-------------------------------------------------------------------------------------------------|------|

|          |                                                                |                                               |    |                                                                                                 | 02FF |

|          |                                                                |                                               |    | Expanded 768 byte (Accessed by direct external addressing mode, by instruction MOVX)  (OME = 1) |      |

|          |                                                                |                                               | FF | (OIVIL - 1)                                                                                     |      |

| 80       | Higher 128 byte (Accessed by indirect addressing mode only)    | SFR (Accessed by direct addressing mode only) |    |                                                                                                 |      |

| 7F<br>00 | Lower 128 byte (Accessed by direct & indirect addressing mode) |                                               | 80 |                                                                                                 | 0000 |

### 1.2.1 Data Memory - Lower 128 byte (\$00 to \$7F, Bank 0 & Bank 1)

Data Memory \$00 to \$FF is the same as 8052.

The address \$00 to \$7F can be accessed by direct and indirect addressing modes.

Address \$00 to \$1F is register area.

Address \$20 to \$2F is memory bit area.

Address \$30 to \$7F is for general memory area.

#### 1.2.2 Data Memory - Higher 128 byte (\$80 to \$FF, Bank 2 & Bank 3)

The address \$80 to \$FF can be accessed by indirect addressing mode or by bank mapping direct addressing mode. Address \$80 to \$FF is data area.

#### 1.2.3 Data Memory - Expanded 768 bytes (\$0000 to \$02FF, Bank 4 ~ Bank 15)

From external address \$0000 to \$02FF is the on-chip expanded RAM area, total 768 bytes. This area can be accessed by external direct addressing mode (by instruction MOVX) or by bank mapping direct addressing mode.

If the address of instruction MOVX @DPTR is larger than \$02FF then SM5964 will generate the external memory control signal automatically. The bit 1 (OME) of special function register \$BF (SCONF) can enable or disable this expanded 768 byte RAM. The default setting of OME bit is 1 (enable).

The address space of instruction MOVX @Ri, i=0,1 is determined by bit 1 & bit 0 (RAMS1, RAMS0) of special function register \$85 (RCON). The default setting of RAMS1, RAMS0 bits is 00 (page0).

One page of data RAM is 256 byte.

RAMS1, RAMS0=00, Rn of instruction MOVX @Ri, i=0,1 mapping to expanded RAM address \$0000 to \$00FF (page 0) RAMS1, RAMS0=01, Rn of instruction MOVX @Ri, i=0,1 mapping to expanded RAM address \$0100 to \$01FF (page 1) RAMS1, RAMS0=10, Rn of instruction MOVX @Ri, i=0,1 mapping to expanded RAM address \$0200 to \$02FF (page 2) RAMS1, RAMS0=11, Rn of instruction MOVX @Ri, i=0,1 mapping to expanded RAM address \$XY00 to \$XYFF which high byte address specified by port 2. (SM5964 will generate the external memory control signal automatically).

#### 1.3 Bank mapping direct addressing mode:

We provide RAM bank address '40H~7FH' as mapping window which allow user access all the 1K on-chip RAM through this RAM bank address.

| BS3 | BS2 | BS1 | BS0 | 040h~07fh map-<br>ping address | Note                          |

|-----|-----|-----|-----|--------------------------------|-------------------------------|

| 0   | 0   | 0   | 0   | 000h~03fh                      | lower 128 byte RAM            |

| 0   | 0   | 0   | 1   | 040h~07fh                      | lower 128 byte RAM            |

| 0   | 0   | 1   | 0   | 080h~0bfh                      | higher 128 byte RAM           |

| 0   | 0   | 1   | 1   | 0c0h~0ffh                      | higher 128 byte RAM           |

| 0   | 1   | 0   | 0   | 0000h~003fh                    | on-chip expanded 768 byte RAM |

| 0   | 1   | 0   | 1   | 0040h~007fh                    | on-chip expanded 768 byte RAM |

| 0   | 1   | 1   | 0   | 0080h~00bfh                    | on-chip expanded 768 byte RAM |

| 0   | 1   | 1   | 1   | 00c0h~00ffh                    | on-chip expanded 768 byte RAM |

| 1   | 0   | 0   | 0   | 0100h~013fh                    | on-chip expanded 768 byte RAM |

| 1   | 0   | 0   | 1   | 0140h~017fh                    | on-chip expanded 768 byte RAM |

| 1   | 0   | 1   | 0   | 0180h~01bfh                    | on-chip expanded 768 byte RAM |

| 1   | 0   | 1   | 1   | 01c0h~01ffh                    | on-chip expanded 768 byte RAM |

| 1   | 1   | 0   | 0   | 0200h~023fh                    | on-chip expanded 768 byte RAM |

| 1   | 1   | 0   | 1   | 0240h~027fh                    | on-chip expanded 768 byte RAM |

| 1   | 1   | 1   | 0   | 0280h~02bfh                    | on-chip expanded 768 byte RAM |

| 1   | 1   | 1   | 1   | 02c0h~02ffh                    | on-chip expanded 768 byte RAM |

With this bank mapping scheme, user can access entire 1k byte on-chip RAM with direct addressing method. That means using the window area (\$040~\$07F), user can access any bank (64 byte) data of 1k byte on-chip RAM space which is selected by BS[0:3] of data bank control register (DBANK, \$86).

For example, user write #30h to \$101 address:

MOV DBANK, #88H ; set bank mapping \$040~\$07f to \$0100~\$013f

MOV A, #30H ; store #30H to A

MOV 41H, A ; write #30H to \$0101 address

#### Data Bank Control Register (DBANK, \$86)

bit-7 bit-0

| Read :        | BSE | Unused | Unused | Unused | BS3 | BS2 | BS1 | BS0 |

|---------------|-----|--------|--------|--------|-----|-----|-----|-----|

| Write:        | 501 | 011000 | 011000 | 011000 | 100 | 301 | 10. | 100 |

| Reset value : | 0   | *      | *      | *      | 0   | 0   | 0   | 1   |

Data bank select enable bit BSE = 1 enables the data bank select function

Data bank select enable bit BSE = 0 disables the data bank select function

BS[3:0] setting will map \$040~\$07F RAM space to entire 1k byte on-chip RAM space.

### Internal RAM Control Register (RCON, \$85)

|              | bit-7   |         |        |         |         |         |        | bit-0    |   |

|--------------|---------|---------|--------|---------|---------|---------|--------|----------|---|

| Read:        | Unused  | Unused  | Unused | Unused  | Unused  | Unused  | RAMS1  | RAMS0    |   |

| Write:       | Officed | Officed | Ondsed | Offuseu | Offuseu | Offuseu | TCIVIO | TVAIVIOU |   |

| Reset value: | *       | *       | *      | *       | *       | *       | 0      | 0        | ] |

Note: "R" means reserved

SM5964 has 768 byte on-chip RAM which can be accessed by external memory addressing method only. (By instruction MOVX). The address space of instruction MOVX @Rn is determined by bit 1 and bit 0 (RAMS1, RAMS0) of RCON. The default setting of RAMS1, RAMS0 bits is 00 (page0).

# System Control Register (SCONF, \$BF)

|                 | DIT-/ |        |        |        |        |      |     | DIT-U |

|-----------------|-------|--------|--------|--------|--------|------|-----|-------|

| Read:<br>Write: | WDR   | Unused | Unused | Unused | Unused | ISPE | OME | ALEI  |

| Reset value:    | 0     | *      | *      | *      | *      | 0    | 1   | 0     |

WDR: Watch Dog Timer Reset. When system reset by Watch Dog Timer overflow, WDR will be set to 1

ISPE: ISP function enable bit

OME: 768 byte on-chip RAM enable bit ALEI: ALE output inhibit bit, to reduce EMI

Setting bit 0 (ALEI) of SCONF can inhibit the clock signal in Fosc/6Hz output to the ALE pin.

The bit 1 (OME) of SCONF can enable or disable the on-chip expanded 768 byte RAM. The default setting of OME bit is 1 (enable).

The bit 7 (WDR) of SCONF is Watch Dog Timer Reset bit. It will be set to 1 when reset signal generated by WDT overflow. User should check WDR bit whenever unpredicted reset happened.

#### 2. Port 4 for PLCC or QFP package:

The bit addressable port 4 is available with PLCC or QFP package. The port 4 has only 4 pins and its port address is located at 0D8H. The function of port 4 is the same as the function of port 1, port 2 and port 3.

#### Port4 (P4, \$D8)

|                   | bit-/  |        |        |        |      |      |      | bit-0 |

|-------------------|--------|--------|--------|--------|------|------|------|-------|

| Read :<br>Write : | Unused | Unused | Unused | Unused | P4.3 | P4.2 | P4.1 | P4.0  |

| Reset value :     | *      | *      | *      | *      | 1    | 1    | 1    | 1     |

The bit 3, bit 2, bit 1, bit 0 output the setting to pin P4.3, P4.2, P4.1, P4.0 respectively.

### 3. In-System Programming (ISP) Function

The SM5964 can generate flash control signal by internal hardware circuit. User utilize flash control register, flash address register and flash data register to perform the ISP function without removing the SM5964 from the system.

The SM5964 provides internal flash control signals which can do flash program/chip erase/page erase/protect functions. User need to design and use any kind of interface which SM5964 can input data. User then utilize ISP service program to perform the flash program/chip erase/page erase/protect functions.

#### 3.1 ISP Service Program

The ISP service program is a user developed firmware program which resides in the ISP service program space. After user developed the ISP service program, user then determine the size of the ISP service program. User need to program the ISP service program in the SM5964 for the ISP purpose.

The ISP service program were developed by user so that it should includes any features which relates to the flash memory programming function as well as communication protocol between SM5964 and host device which output data to the SM5964. For example, if user utilize UART interface to receive/transmit data between SM5964 and host device, the ISP service program should include baut rate, checksum or parity check or any error-checking mechanism to avoid data transmission error.

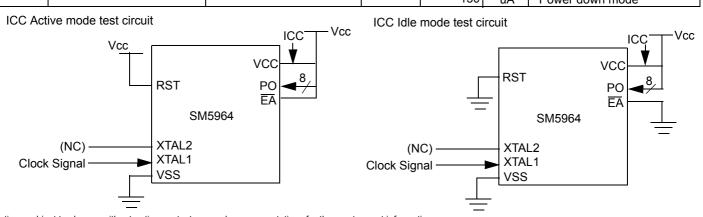

The ISP service program can be initiated under SM5964 active or idle mode. It can not be initiated under power down mode.

#### 3.2. Lock Bit (N)

The Lock Bit N has two functions: one is for service program size configuration and the other is to lock the ISP service program space from flash erase function.

The ISP service program space address range \$F000 to \$FFFF. It can be divided as blocks of N\*512 byte. (N=0 to 8). When N=0 means no ISP function, all of 64K byte flash memory can be used as program memory. When N=1 means ISP service program occupies 512 byte while the rest of 63.5K byte flash memory can be used as program memory. The maximum ISP service program allowed is 4K byte when N=8. Under such configuration, the usable program memory space is 60K byte.

After N determined, SM5964 will reserve the ISP service program space downward from the top of the program address \$FFFF. The start address of the ISP service program located at \$Fx00 while x is an even number, depending on the lock bit N. Please see page 5 program memory diagram for this ISP service program space structure.

10/28

The lock bit N function is different from the flash protect function. The flash erase function can erase all of the flash memory except for the locked ISP service program space. If the flash not been protected, the content of ISP service program still can be read. If the flash been protected, the overall content of flash program memory space including ISP service program space can not be read.

# 3.3 Program the ISP Service Program

After Lock Bit N is set and ISP service program been programmed, the ISP service program memory will be protected (locked) automatically. The lock bit N has its own program/erase timing. It is different from the flash memory program/erase timing so the locked ISP service program can not be erased by flash erase function. If user need to erase the locked ISP service program, he can do it by writer only. User can not change ISP service program when SM5964 was in system.

# 3.4 Initiate ISP Service Program

To initiate the ISP service program is to load the program counter (PC) with start address of ISP service program and execute it. There are two ways to do so:

- (1) Blank reset. Hardware reset with first flash address blank (\$0000=#FFH) will load the PC with start address of ISP service program.

- (2) Execute jump instruction can load the start address of the ISP service program to PC.

User can initiate general 8052 INT function to initiate the ISP service program. After ISP service program executed, user need to reset the SM5964, either by hardware reset or by WDT, or jump to the address \$0000 to re-start the firmware program.

#### ISP Registers - ISPFAH, ISPFAL, ISPFD and ISPC

#### ISP Flash Address-High Register (ISPFAH, \$F4)

|              | Dit-/ |      |      |      |      |      |       | Dit-U |

|--------------|-------|------|------|------|------|------|-------|-------|

| Read:        | FA15  | FA14 | FA13 | FA12 | FA11 | FA10 | FA9   | FA8   |

| Write:       | 1713  | 1714 | 1713 | 1712 | 1711 | 1710 | 1 / 3 | 1 70  |

| Reset value: | 0     | 0    | 0    | 0    | 0    | 0    | 0     | 0     |

FA15 ~ FA8: flash address-high for ISP function

#### ISP Flash Address-Low Register (ISPFAL, \$F5)

|              | Dit-/ |     |     |       |     |      |     | Dit-U |

|--------------|-------|-----|-----|-------|-----|------|-----|-------|

| Read:        | FA7   | FA6 | FA5 | FA4   | FA3 | FA2  | FA1 | FA0   |

| Write:       | IA    | 170 | 175 | 1 //4 | 173 | 1 72 | IAI | 1 70  |

| Reset value: | 0     | 0   | 0   | 0     | 0   | 0    | 0   | 0     |

FA7 ~ FA0: flash address-low for ISP function

The ISPFAH & ISPFAL provide the 16-bit flash memory address for ISP function. The flash memory address should not include the ISP service program space address. If the flash memory address indicated by ISPFAH & ISPFAL registers

overlay with the ISP service program space address, the flash program/page erase of ISP function executed thereafter will have no effect.

#### ISP Flash Data Register (ISPFD,\$F6)

|                 | bit-7 |     |     |     |     |     |     | bit-0 |

|-----------------|-------|-----|-----|-----|-----|-----|-----|-------|

| Read:<br>Write: | FD7   | FD6 | FD5 | FD4 | FD3 | FD2 | FD1 | FD0   |

| Reset value:    | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |

FD7 ~ FD0: flash data for ISP function

The ISPFD provide the 8-bit data for ISP function.

#### ISP Flash Control Register (ISPC, \$F7)

|                 | bit-7 |        |        |        |        |        |    | bit-0 |

|-----------------|-------|--------|--------|--------|--------|--------|----|-------|

| Read:<br>Write: | START | Unused | Unused | Unused | Unused | Unused | F1 | F0    |

| Reset value:    | 0     | *      | *      | *      | *      | *      | 0  | 0     |

F[1: 0]: ISP function select bit START: ISP function start bit

= 1 : start ISP function which indicated by bit 1, bit 0 (F1, F0)

= 0 : no operation

The START bit is read-only by default, software must write three specific values 55H, AAH and 55H sequentially to the ISPFD register to enable the START bit write attribute. That is :

MOV ISPFD, #55H MOV ISPFD, #AAH MOV ISPFD, #55H

Any attempt to set START bit will not be allowed without the procedure above.

After START bit set to 1 then the SM5964 hardware circuit will latch address and data bus and hold the program counter until the START bit reset to 0 when ISP function finished. User does not need to check START bit status by software method.

| F[1:0] | ISP function |

|--------|--------------|

| 00     | Byte program |

| 01     | Chip protect |

| 10     | Page erase   |

| 11     | Chip erase   |

F[1:0]: ISP function select bit

One page of flash memory is 512 byte.

To perform byte program/page erase ISP function, user need to specify flash address at first. When performing page erase function, SM5964 will erase entire page which flash address indicated by ISPFAH & ISPFAL registers located within the page. e.g. flash address: \$XYMN

page erase function will erase from \$XY00 to \$X(Y+1)FF (Y:even number), or page erase function will erase from \$X(Y-1) 00 to \$XYFF (Y:odd number)

To perform the chip erase ISP function, SM5964 will erase all the flash program memory except the ISP service program space, also, SM5964 will un-protect the flash memory automatically. To perform chip protect ISP function, the SM5964 flash memory content will be read #00H.

e.g. ISP service program to do the byte program - to program #22H to the address \$1005H

MOV SCONF,#04H ; enable SM5964 ISP function MOV ISPFAH,#10H ; set flash address-high, 10H MOV ISPFAL.#05H ; set flash address-low, 05H

MOV ISPFD,#22H ; set flash data to be programmed, data = 22H MOV ISPC,#80H ; start to program #22H to the flash address \$1005H

; after byte program finished, START bit of ISPC will be reset to 0 automatically

; program counter then point to the next instruction

# ISP Registers - System Control Register (SCONF,\$BF)

bit-7 bit-0

WDR Unused Unused Unused ISPE OME ALEI

Write:

0

\*

\*

\*

0

1

0

The bit 2 (ISPE) of SCONF is ISP enable bit. User can enable overall SM5964 ISP function by setting ISPE bit to 1, to disable overall ISP function by set ISPE to 0.

The function of ISPE behaves like a security key. User can disable overall ISP function to prevent software program be erased accidentally.

#### 4. Watch Dog Timer

Read:

The Watch Dog Timer (WDT) is a 16-bit free-running counter that generate reset signal if the counter overflows. The WDT is useful for systems which are susceptible to noise, power glitches, or electronics discharge which causing software dead loop or runaway. The WDT function can help user software recover form abnormal software condition. The WDT is different from Timer0, Timer1 and Timer2 of general 8052. To prevent a WDT reset can be done by software periodically clearing the WDT counter. User should check WDR bit of SCONF register whenever unpredicted reset happened

The WDT has selectable divider input for the time base source clock. To select the divider input, the setting of bit2~bit0 (PS2~PS0) of Watch Dog Timer Control Register (WDTC) should be set accordingly.

To enable the WDT is done by setting 1 to the bit 7 (WDTE) of WDTC. After WDTE set to 1, the 16-bit counter starts to count with the selected time base source clock which set by PS2~PS0. It will generate a reset signal when overflows. The WDTE bit will be cleared to 0 automatically when SM5964 been reset, either hardware reset or WDT reset.

To reset the WDT is done by setting 1 to the CLEAR bit of WDTC. This will clear the content of the 16-bit counter and let the counter re-start to count from the beginning.

### 4.1 Watch Dog Timer Registers: WDTC and SCONF

### Watch Dog Timer Register- WDT Control Register (WDTC, \$9F)

bit-7 bit-0 Read: WDTE Unused **CLEAR** Unused Unused PS2 PS1 PS0 Write: 0 0 0 0 0 Reset value:

WDTE: Watch Dog Timer enable bit CLEAR: Watch Dog Timer counter clear bit

PS[2:0]: clock source divider bit

| PS [2:0] | Divider (OSC in) | Time Period (ms) @40MHZ |

|----------|------------------|-------------------------|

| 000      | 8                | 13.1                    |

| 001      | 16               | 26.21                   |

| 010      | 32               | 52.42                   |

| 011      | 64               | 104.8                   |

| 100      | 128              | 209.71                  |

| 101      | 256              | 419.43                  |

| 110      | 512              | 838.86                  |

| 111      | 1024             | 1677.72                 |

#### Watch Dog Timer Register - System Control Register (SCONF, \$BF)

|                 | bit-7 |        |        |        |        |      |     | bit-0 |

|-----------------|-------|--------|--------|--------|--------|------|-----|-------|

| Read:<br>Write: | WDR   | Unused | Unused | Unused | Unused | ISPE | OME | ALEI  |

| Reset value:    | 0     | *      | *      | *      | *      | 0    | 1   | 0     |

The bit 7 (WDR) of SCONF is Watch Dog Timer Reset bit. It will be set to 1 when reset signal generated by WDT overflow. User should check WDR bit whenever unpredicted reset happened

#### 5. Reduce EMI Function

The SM5964 allows user to reduce the EMI emission by setting 1 to the bit 0 (ALEI) of SCONF register. This function will inhibit the clock signal in Fosc/6Hz output to the ALE pin.

# 6. Specific Pulse Width Modulation (SPWM)

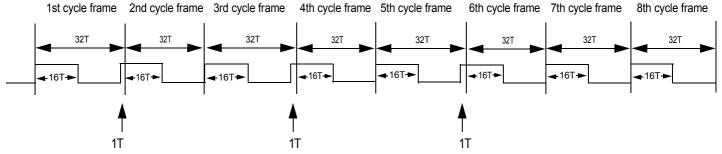

The Specific Pulse Width Modulation (SPWM) module has five 8-bit channels, each channel contains a 8-bit wide SPWM data register (SPWMD) to decide number of continuous pulses within a SPWM frame cycle.

#### **6.1 SPWM Function Description:**

Each 8-bit SPWM channel is composed of an 8-bit register which contains a 5-bit SPWM in MSB portion and a 3-bit binary rate multiplier (BRM) in LSB portion. The value programmed in the 5-bit SPWM portion will determine the pulse length of the output. The 3-bit BRM portion will generate and insert certain narrow pulses among an 8-SPWM-cycle frame. The number of pulses generated is equal to the number programmed in the 3-bit BRM portion. The usage of the BRM is to generate equivalent 8-bit resolution SPWM type DAC with reasonably high repetition rate through 5-bit SPWM clock speed. The PDIV[1:0] settings of SPWMC (\$A3) register are divident of Fosc to be SPWM clock, Fosc/2^(PDIV[1:0]+1). The SPWM output cycle frame repetition rate (frequency) equals (SPWM clock)/32 which is [Fosc/2^(PDIV[1:0]+1)]/32.

### 6.2 SPWM Registers - P1CON, SPWMC, SPWMR[4:0]

### SPWM Registers - Port1 Configuration Register (P1CON, \$9B)

|                 | bit-7  |        |        |        |        |        |        | bit-0  |

|-----------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Read:<br>Write: | SPWM4E | SPWM3E | SPWM2E | SPWM1E | SPWM0E | Unused | Unused | Unused |

| Reset value:    | 0      | 0      | 0      | 0      | 0      | *      | *      | *      |

SPWM[4:0]E: When the bit set to one, the corresponding SPWM pin is active as SPWM function. When the bit reset to zero, the corresponding SPWM pin is active as I/O pin. Five bits are cleared upon reset.

#### SPWM Registers - SPWM Control Register (SPWMC, \$A3)

|                 | bit-7  |        |        |        |        |        |       | bit-0 |  |

|-----------------|--------|--------|--------|--------|--------|--------|-------|-------|--|

| Read:<br>Write: | Unused | Unused | Unused | Unused | Unused | Unused | PDIV1 | PDIV0 |  |

| Reset value:    | *      | *      | *      | *      | *      | *      | 0     | 0     |  |

PDIV[1:0]: These two bits is 2's power parameter to form a frequency divider for input clock.

| PDIV1 | PDIV0 | Divider | SPWM clock, Fosc=20MHz | SPWM clock, Fosc=24MHz |

|-------|-------|---------|------------------------|------------------------|

| 0     | 0     | 2       | 10MHz                  | 12MHz                  |

| 0     | 1     | 4       | 5MHz                   | 6MHz                   |

| 1     | 0     | 8       | 2.5MHz                 | 3MHz                   |

| 1     | 1     | 16      | 1.25MHz                | 1.5MHz                 |

# SPWM Data Register (SPWMD[4:0], \$AC, \$A4 ~\$A7)

0

bit-7 bit-0 Read: **SPWMD SPWMD SPWMD SPWMD SPWMD** BRM **BRM BRM** [4:0]4 [4:0]3 [4:0]2 [4:0]1 [4:0]0 [4:0]2 [4:0]1 [4:0]0 Write:

0

0

0

SPWMD[4:0][4:0] : content of SPWM Data Register. It determines duty cycle of SPWM output waveform.

BRM[4:0][2:0]: will insert certain narrow pulses among an 8-SPWM-cycle frame

0

| N = BRM[4:0][2:0] | Number of SPWM cycles inserted in an 8-cycle frame |

|-------------------|----------------------------------------------------|

| XX1               | 1                                                  |

| X1X               | 2                                                  |

| 1XX               | 4                                                  |

# **Example of SPWM timing diagram:**

Reset value:

MOV SPWMD0, #83H ; SPWMD0[4:0]=10h (=16T high, 16T low), BRM0[2:0] = 3

MOV P1CON, #08H; Enable P1.3 as PWM output pin

(narrow pulse inserted by BRM0[2:0] setting, here BRM0[2:0]=3)

SPWM clock =  $1/T = Fosc/2^{(PDIV+1)}$

The SPWM output cycle frame frequency = SPWM clock / 32 = [Fosc/2^(PDIV+1)]/32

If user use Fosc=20MHz, PDIV[1:0] of SPWMC=#03H, then SPWM clock = 20MHz/2^4 = 20MHz/16 = 1.25MHz SPWM output cycle frame frequency = (20MHz/2^4)/32=39.1KHz

# **Operating Conditions**

| Symbol  | Description           | Min. | Тур. | Max. | Unit. | Remarks                        |

|---------|-----------------------|------|------|------|-------|--------------------------------|

| TA      | Operating temperature | 0    | 25   | 70   | °C    | Ambient temperature under bias |

| TS      | Storage temperature   | -55  | 25   | 155  | °C    |                                |

| VCC5    | Supply voltage        | 4.5  | 5.0  | 5.5  | V     |                                |

| Fosc 16 | Oscillator Frequency  | 3.0  | 16   | 16   | MHz   | For 5V application             |

| Fosc 25 | Oscillator Frequency  | 3.0  | 25   | 25   | MHz   | For 5V application             |

| Fosc 40 | Oscillator Frequency  | 3.0  | 40   | 40   | MHz   | For 5V application             |

# **DC** Characteristics

(16/25/40 MHZ, typical operating conditions, valid for SM5964series)

| Symbol | Parameter                  | Valid                  | Min.   | Max.        | Unit     | Test Conditions                   |

|--------|----------------------------|------------------------|--------|-------------|----------|-----------------------------------|

| VIL1   | Input Low Voltage          | port 0,1,2,3,4,#EA     | -0.5   | 1.0         | V        | Vcc=5V                            |

| VIL2   | Input Low Voltage          | RES, XTAL1             | 0      | 0.8         | V        | cc                                |

| VIH1   | Input High Voltage         | port 0,1,2,3,4,#EA     | 2.0    | Vcc+0.5     | V        | u                                 |

| VIH2   | Input High Voltage         | RES, XTAL1             | 70%Vcc | Vcc+0.5     | <b>V</b> | cc                                |

| VOL1   | Output Low Voltage         | port 0, ALE, #PSEN     |        | 0.45        | V        | IOL=3.2mA                         |

| VOL2   | Output Low Voltage         | port 1,2,3,4           |        | 0.45        | V        | IOL=1.6mA                         |

| VOH1   | Output High Voltage        | port 0                 | 2.4    |             | V        | IOH=-800uA                        |

|        |                            |                        | 90%Vcc |             | V        | IOH=-80uA                         |

| VOH2   | Output High Voltage        | port 1,2,3,4,ALE,#PSEN | 2.4    |             | V        | IOH=-60uA                         |

|        |                            |                        | 90%Vcc |             | V        | IOH=-10uA                         |

| IIL    | Logical 0 Input Current    | port 1,2,3,4           |        | -75         | uA       | Vin=0.45V                         |

| ITL    | Logical Transition Current | port 1,2,3,4           |        | -650        | uA       | Vin=2.0V                          |

| ILI    | Input Leakage Current      | port 0, #EA            |        | <u>+</u> 10 | uA       | 0.45V <vin<vcc< td=""></vin<vcc<> |

| R RES  | Reset Pulldown Resistance  | RES                    | 50     | 300         | Kohm     |                                   |

| C IO   | Pin Capacitance            |                        |        | 10          | pF       | Freq=1MHz, Ta=25℃                 |

| ICC    | Power Supply Current       | Vdd                    |        | 20          | mA       | Active mode, 40MHz                |

|        |                            |                        |        | 15          | mA       | Active mode, 25MHz                |

|        |                            |                        |        | 10          | mA       | Active mode, 16MHz                |

|        |                            |                        |        | 10          | mA       | Idle mode, 40MHz                  |

|        |                            |                        |        | 7.5         | mA       | Idle mode, 25MHz                  |

|        |                            |                        |        | 6           | mA       | Idle mode, 16MHz                  |

|        |                            |                        |        | 150         |          | Power down mode                   |

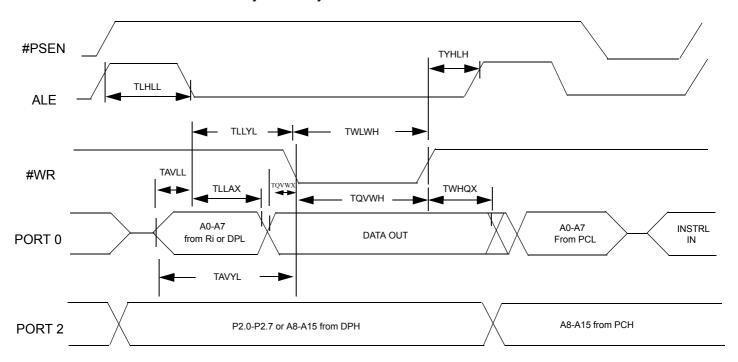

# **AC Characteristics**

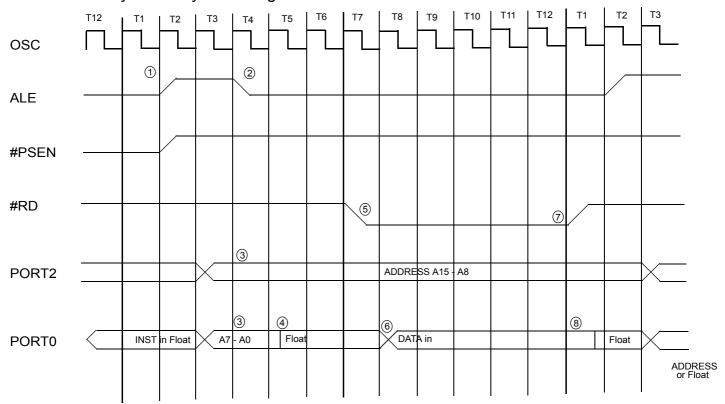

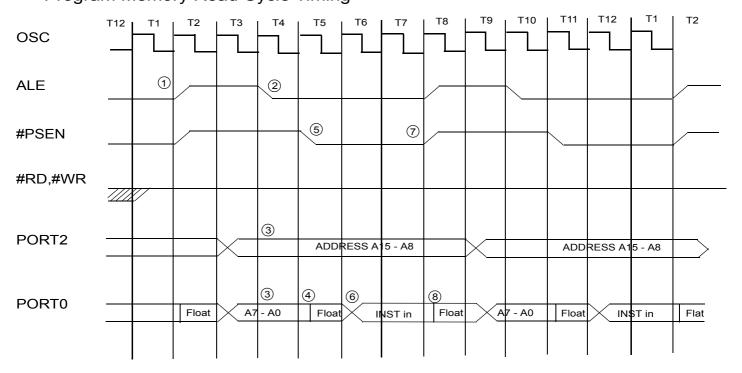

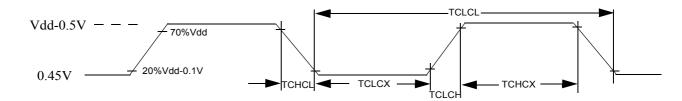

(16/25/40 MHZ, operating conditions; CL for Port 0, ALE and PSEN Outputs=150uF; CL for all Other Output=80pF)

| T LLAX         Address Hold after ALE Iow         RD/WRT         53         T - 10         nS           T LLIV         ALE Iow to Valid Instruction In         RD         240         4xT - 10         nS           T LLPL         ALE Iow to #PSEN Iow         RD         53         T - 10         nS           T PLPH         #PSEN pulse width         RD         173         3xT - 15         nS           T PLIV         #PSEN low to Valid Instruction In         RD         177         3xT - 10         nS           T PXIX         Instruction Float after #PSEN         RD         0         0         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIZ         Instruction Float after #PSEN         RD         10         10         nS           T PXIZ         Instruction Float after #PSEN         RD         10         10         nS           T PXIZ         PSEN Iow to Address Float         RD         10         nS         5                                                                                                                                                           |          |                                   | Valid  | f osc 16 |      | Variable f osc |          | Unit   | Remarks  |    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|--------|----------|------|----------------|----------|--------|----------|----|--|

| T AVLL         Address Valid to ALE low         RD/WRT         43         T - 20         nS           T LLIAX         Address Hold after ALE low         RD/WRT         53         T - 10         nS           T LLIV         ALE low to Valid Instruction In         RD         240         4xT - 10         nS           T LLIPL         ALE low to #PSEN low         RD         53         T - 10         nS           T PLPH         #PSEN pulse width         RD         173         3xT - 15         nS           T PLIV         #PSEN low to Valid Instruction In         RD         177         3xT - 10         nS           T PXIX         Instruction Float after #PSEN         RD         0         0         nS           T PXIX         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIX         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIX         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIX         Instruction Float after #PSEN         RD         10         nS         5xT - 20         nS           T PXIZ         #PSEN low to Address Float         RD         10                                                                                                                                                         | -        |                                   | -      | Min.     | Тур. | Max            |          | Тур.   | Max      |    |  |

| T LLAX         Address Hold after ALE Iow         RD/WRT         53         T - 10         nS           T LLIV         ALE Iow to Valid Instruction In         RD         240         4xT - 10         nS           T LLPL         ALE Iow to #PSEN Iow         RD         53         T - 10         nS           T PLPH         #PSEN pulse width         RD         173         3xT - 15         nS           T PLIV         #PSEN low to Valid Instruction In         RD         177         3xT - 10         nS           T PXIX         Instruction Float after #PSEN         RD         0         0         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T PXIZ         Instruction Float after #PSEN         RD         10         10         nS           T PXIZ         Instruction Float after #PSEN         RD         10         10         nS           T PXIZ         PSEN Iow to Address Float         RD         10         nS         5                                                                                                                                                           |          | I                                 | RD/WRT | 115      |      |                | 2xT - 10 |        |          | nS |  |

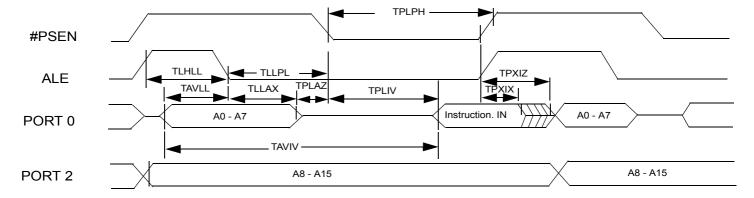

| T LLIV         ALE low to Valid Instruction In         RD         240         4xT - 10         nS           T LLPL         ALE low to #PSEN low         RD         53         T - 10         nS           T PLIV         #PSEN pulse width         RD         173         3xT - 15         nS           T PLIV         #PSEN low to Valid Instruction In         RD         177         3xT - 10         nS           T PXIX         Instruction Hold after #PSEN         RD         0         nS         T + 25         nS           T PXIX         Instruction Float after #PSEN         RD         87         T + 25         nS           T AVIV         Address to Valid Instruction In         RD         87         T + 25         nS           T AVIV         Address to Valid Instruction In         RD         292         5xT - 20         nS           T AVIV         Address to Valid Instruction In         RD         10         10         nS           T RLADY         #PSEN low to Address Float         RD         10         nS         5xT - 20         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Float after #RD         RD                                                                                                                                                            | T AVLL   | Address Valid to ALE low          | RD/WRT | 43       |      |                | T - 20   |        |          | nS |  |

| T LLPL         ALE low to #PSEN low         RD         53         T - 10         nS           T PLPH         #PSEN pulse width         RD         173         3xT - 15         nS           T PLIV         #PSEN low to Valid Instruction In         RD         177         3xT - 10         nS           T PXIX         Instruction Hold after #PSEN         RD         0         0         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T AVIV         Address to Valid Instruction In         RD         292         5xT - 20         nS           T AVIV         Address to Valid Instruction In         RD         10         10         nS           T AVIV         Address to Valid Instruction In         RD         292         5xT - 20         nS           T PLAZ         #PSEN low to Address Float         RD         10         nS         5xT - 20         nS           T RLDX         #RD pulse width         WRT         365         6xT - 10         nS         nS           T RLPA         #RD pulse width         WRT         365         6xT - 10         nS         nS           T RLDV         #RD low to Valid Data In         RD                                                                                                                                                                       | T LLAX   | Address Hold after ALE low        | RD/WRT | 53       |      |                | T - 10   |        |          | nS |  |

| T PLPH         #PSEN pulse width         RD         173         3xT - 15         nS           T PLIV         #PSEN low to Valid Instruction In         RD         177         3xT - 10         nS           T PXIX         Instruction Hold after #PSEN         RD         0         0         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T AVIV         Address to Valid Instruction In         RD         292         5xT - 20         nS           T PLAZ         #PSEN low to Address Float         RD         10         n         nS           T PLAZ         #PSEN low to Address Float         RD         10         nS         10           T RLAH         #RD pulse width         RD         365         6xT - 10         nS           T RLHP         #WR pulse width         WRT         365         6xT - 10         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS <tr< td=""><td>T LLIV</td><td>ALE low to Valid Instruction In</td><td>RD</td><td></td><td></td><td>240</td><td></td><td></td><td>4xT - 10</td><td>nS</td><td></td></tr<>         | T LLIV   | ALE low to Valid Instruction In   | RD     |          |      | 240            |          |        | 4xT - 10 | nS |  |

| T PLIV         #PSEN low to Valid Instruction In RD         177         3xT - 10         nS           T PXIX         Instruction Hold after #PSEN         RD         0         0         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T AVIV         Address to Valid Instruction In         RD         292         5xT - 20         nS           T PLAZ         #PSEN low to Address Float         RD         10         10         nS           T RLRH         #RD pulse width         RD         365         6xT - 10         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDX         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT                                                                                                                                                           | T LLPL   | ALE low to #PSEN low              | RD     |          |      |                | T - 10   |        |          | nS |  |

| T PXIX         Instruction Hold after #PSEN         RD         0         0         nS           T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T AVIV         Address to Valid Instruction In         RD         292         5xT - 20         nS           T PLAZ         #PSEN low to Address Float         RD         10         10         nS           T RLPA         #RD pulse width         RD         365         6xT - 10         nS           T RLPW         #WR pulse width         WRT         365         6xT - 10         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDX         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT                                                                                                                                                                    | T PLPH   | #PSEN pulse width                 | RD     | 173      |      |                | 3xT - 15 |        |          | nS |  |

| T PXIZ         Instruction Float after #PSEN         RD         87         T + 25         nS           T AVIV         Address to Valid Instruction In         RD         292         5xT - 20         nS           T PLAZ         #PSEN low to Address Float         RD         10         10         nS           T RLRH         #RD pulse width         RD         365         6xT - 10         nS           T WLWH         #WR pulse width         WRT         365         6xT - 10         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDZ         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T QVWH         Data Valid to #WR High         WRT         403 <td< td=""><td>T PLIV</td><td>#PSEN low to Valid Instruction In</td><td>RD</td><td></td><td></td><td>177</td><td></td><td></td><td>3xT - 10</td><td>nS</td><td></td></td<> | T PLIV   | #PSEN low to Valid Instruction In | RD     |          |      | 177            |          |        | 3xT - 10 | nS |  |

| T AVIV         Address to Valid Instruction In         RD         292         5xT - 20         nS           T PLAZ         #PSEN low to Address Float         RD         10         10         nS           T RLRH         #RD pulse width         RD         365         6xT - 10         nS           T WLWH         #WR pulse width         WRT         365         6xT - 10         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDZ         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         73         <                                                                                                                                                                | T PXIX   | Instruction Hold after #PSEN      | RD     | 0        |      |                | 0        |        |          | nS |  |

| T PLAZ         #PSEN low to Address Float         RD         10         10         nS           T RLRH         #RD pulse width         RD         365         6xT - 10         nS           T WLWH         #WR pulse width         WRT         365         6xT - 10         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDZ         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QWWH         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73 <td< td=""><td>T PXIZ</td><td>Instruction Float after #PSEN</td><td>RD</td><td></td><td></td><td>87</td><td></td><td></td><td>T + 25</td><td>nS</td><td></td></td<>        | T PXIZ   | Instruction Float after #PSEN     | RD     |          |      | 87             |          |        | T + 25   | nS |  |

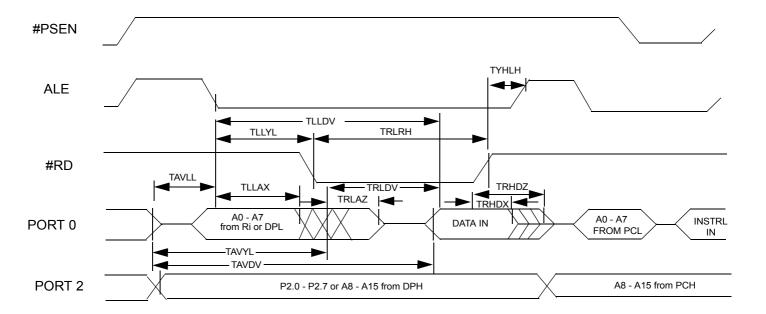

| T RLRH         #RD pulse width         RD         365         6xT - 10         nS           T WLWH         #WR pulse width         WRT         365         6xT - 10         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDZ         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR transition         WRT         403         7xT - 35         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53                                                                                                                                                                | T AVIV   | Address to Valid Instruction In   | RD     |          |      | 292            |          |        | 5xT - 20 | nS |  |

| T WLWH         #WR pulse width         WRT         365         6xT - 10         nS           T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDZ         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53                                                                                                                                                           | T PLAZ   | #PSEN low to Address Float        | RD     |          |      | 10             |          |        | 10       | nS |  |

| T RLDV         #RD low to Valid Data In         RD         302         5xT - 10         nS           T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDZ         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T CHCZ         #RD low to Address Float         RD         5         nS           T CHCL         clock fall time         nS         T - 10         T + 10                                                                                                                                                                   | T RLRH   | #RD pulse width                   | RD     | 365      |      |                | 6xT - 10 |        |          | nS |  |

| T RHDX         Data Hold after #RD         RD         0         0         nS           T RHDZ         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T YALH         #WR or #RD high to ALE high         RD         5         nS           T CHCL         clock fall time         nS         T - 10         T + 10         nS           T CLCX         clock high time         nS         T - 10         nS <td< td=""><td>T WLWH</td><td>#WR pulse width</td><td>WRT</td><td>365</td><td></td><td></td><td>6xT - 10</td><td></td><td></td><td>nS</td><td></td></td<>                  | T WLWH   | #WR pulse width                   | WRT    | 365      |      |                | 6xT - 10 |        |          | nS |  |

| T RHDZ         Data Float after #RD         RD         145         2xT + 20         nS           T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T RLAZ         #RD low to Address Float         RD         5         nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53         72         T - 10         T + 10         nS           T CHCL         clock fall time         nS         nS         nS         nS           T CLCH         clock high time         nS                                                                                                                                                                     | T RLDV   | #RD low to Valid Data In          | RD     |          |      | 302            |          |        | 5xT - 10 | nS |  |

| T LLDV         ALE low to Valid Data In         RD         590         8xT - 10         nS           T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T RLAZ         #RD low to Address Float         RD         5         nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53         72         T - 10         T + 10         nS           T CHCL         clock fall time         nS         nS         nS         nS           T CLCH         clock high time         nS         nS         nS         nS                                                                                                                                                                                                                                     | T RHDX   | Data Hold after #RD               | RD     | 0        |      |                | 0        |        |          | nS |  |

| T AVDV         Address to Valid Data In         RD         542         9xT - 20         nS           T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T RLAZ         #RD low to Address Float         RD         5         nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53         72         T - 10         T + 10         nS           T CHCL         clock fall time         nS         nS         nS         nS           T CLCX         clock rise time         nS         nS         nS           T CHCX         clock high time         nS         nS                                                                                                                                                                                                                                                                                      | T RHDZ   | Data Float after #RD              | RD     |          |      | 145            |          |        | 2xT + 20 | nS |  |

| T LLYL         ALE low to #WR High or #RD low         RD/WRT         178         197         3xT - 10         3xT + 10         nS           T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T RLAZ         #RD low to Address Float         RD         5         nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53         72         T -10         T + 10         nS           T CHCL         clock fall time         nS         nS         nS         nS           T CLCX         clock low time         nS         nS         nS           T CLCH         clock rise time         nS         nS                                                                                                                                                                                                                                                                                                                                                                                             | T LLDV   | ALE low to Valid Data In          | RD     |          |      | 590            |          |        | 8xT - 10 | nS |  |

| T AVYL         Address Valid to #WR or #RD low         RD/WRT         230         4xT - 20         nS           T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T RLAZ         #RD low to Address Float         RD         5 nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53         72         T -10         T + 10         nS           T CHCL         clock fall time         nS         nS         nS         nS           T CLCX         clock low time         nS         nS         nS           T CLCH         clock rise time         nS         nS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T AVDV   | Address to Valid Data In          | RD     |          |      | 542            |          |        | 9xT - 20 | nS |  |

| T QVWH         Data Valid to #WR High         WRT         403         7xT - 35         nS           T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T RLAZ         #RD low to Address Float         RD         5         nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53         72         T -10         T + 10         nS           T CHCL         clock fall time         nS         nS         nS         nS           T CLCX         clock low time         nS         nS         nS           T CLCH         clock rise time         nS         nS           T CHCX         clock high time         nS         nS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T LLYL   | ALE low to #WR High or #RD low    | RD/WRT | 178      |      | 197            | 3xT - 10 |        | 3xT + 10 | nS |  |

| T QVWX         Data Valid to #WR transition         WRT         38         T - 25         nS           T WHQX         Data hold after #WR         WRT         73         T + 10         nS           T RLAZ         #RD low to Address Float         RD         5 nS           T YALH         #WR or #RD high to ALE high         RD/WRT         53         72         T -10         T + 10 nS           T CHCL         clock fall time         nS         nS           T CLCX         clock low time         nS           T CLCH         clock rise time         nS           T CHCX         clock high time         nS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T AVYL   | Address Valid to #WR or #RD low   | RD/WRT | 230      |      |                | 4xT - 20 |        |          | nS |  |