#### **FEATURES**

- PC half-bridge (or 494) power supply supervisor + two 431 + PWM

- High integration & few external components

- Over-voltage protection for 3.3V, 5V and 12V

- Under-voltage protection for 3.3V, 5V and 12V

- Under-voltage protection for -12V and/or -5V

- Over-power and short-circuit protection

- Power-down warning circuitry

- Power good circuitry

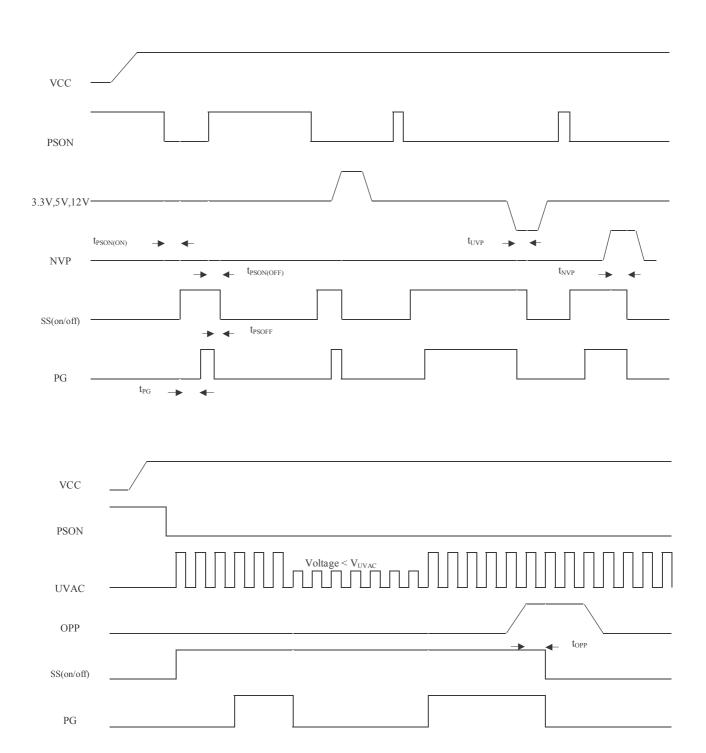

- Delay time for PSON and PG signal

- Remote ON/OFF function

- On-chip oscillator and error amplifier

- Two shunt regulator for 3.3V and 5V-Standby

- Latching PWM for cycle-by-cycle switching

- Push-pull PWM operation and totem pole outputs

- Soft-start and maximum 93% duty cycle

#### **APPLICATIONS**

Switching mode power supply for Computers, such as:

ATX

NLX

SFX (micro-ATX)

#### **DESCRIPTION**

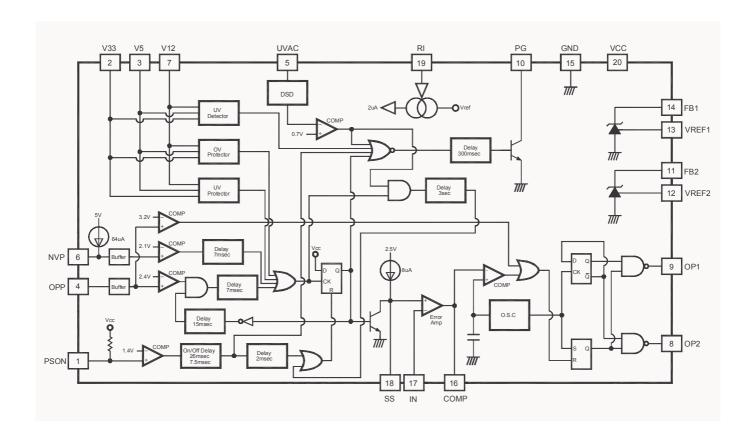

SG6105 controller is designed for switching mode power supply for desktop PCs. It provides all the functions necessary to monitor and control the output of the power supply. Remote ON/OFF control, power good circuitry, some protection features against over-voltage and over-power are implemented. It directly senses all the output rails for OVP without the need of external dividers. An innovated AC-signal sampling circuitry provides a sufficient power-down warning signal for PG. A built-in timer generates accuracy timing for control circuit including the PS-off delay. The cycle-by-cycle PWM switching prevents the power transformer from the saturation and ensures the fastest response for the short-circuit protection which greatly reduce the stress for power transistors. Two internal precision TL431 shunt regulators provide stable reference voltage and driver for 3.3V and 5V-standby regulation. Utilizing minimum number of external components, the SG6105 includes all of the functions for push-pull and/or half-bridge topology, decreasing the production cost and PCB space, and increasing the MTBF for power supply.

## **MARKING DIAGRAMS**

T: D = DIP

P: Z = Lead Free

Null=regular package

XXXXXXX: Wafer Lot

YY: Year; WW: Week

V: Assembly Location

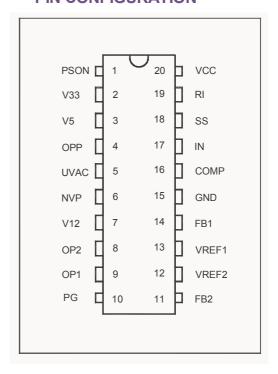

#### PIN CONFIGURATION

# **ORDERING INFORMATION**

| Part Number | Package               |

|-------------|-----------------------|

| SG6105D     | 20-Pin DIP            |

| SG6105DZ    | 20-Pin DIP(Lead Free) |

# **PIN DESCRIPTIONS**

| Name    | Pin | Туре                  | Function                                                                                                                                                                                                                            |

|---------|-----|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC     | 20  | Supply                | Supply voltage. 4.5V ~ 5.5V. It is connected to 5V-standby.                                                                                                                                                                         |

| PG      | 10  | Logic output          | Power Good logic output, 0 or 1 (open-collector). PG = 1 means that the power is good for operation. The PG delay is 300 msec.                                                                                                      |

| V33     | 2   | Analog input          | 3.3V over-voltage/under-voltage control sense input.                                                                                                                                                                                |

| V5      | 3   | Analog input          | 5V over-voltage/under-voltage control sense input.                                                                                                                                                                                  |

| V12     | 7   | Analog input          | 12V over-voltage/under-voltage control sense input.                                                                                                                                                                                 |

| OPP     | 4   | Analog input          | Over-power sense input. This pin is connected to driver transformer or the output of current transformer. When not in use, this pin should be grounded.                                                                             |

| PSON    | 1   | Logic input           | Remote On/Off logic input for CPU or controller. Turn on/off the PWM Output after the 7.5 msec / 26 msec delay.  PSON = 0 means that the main SMPS is operational.  PSON =1 means that the main SMPS is off and the latch is reset. |

| NVP     | 6   | Analog input          | The protection input for negative output, such as $-12V$ and/or $-5V$ . Trip voltage = 2.1V.                                                                                                                                        |

| UVAC    | 5   | Analog input          | AC fail detection, detect main AC voltage under-voltage and/or failure.                                                                                                                                                             |

| COMP    | 16  | Analog output         | Error amplifier output and the input of the PWM comparator.                                                                                                                                                                         |

| IN      | 17  | Analog input          | The negative input of error amplifier. The positive input of error amplifier is a 2.5V reference voltage.                                                                                                                           |

| SS      | 18  | Analog input          | The soft-start. It is settable through external capacitor. The current source output at this pin is 8uA and the voltage is clamped at 2.5V.                                                                                         |

| OP1/OP2 | 9/8 | Analog output         | The totem-pole output drivers of push-pull PWM. The output are enabled (low) only when the NAND gate inputs are high, the maximum duty cycle on an output (OP1 or OP2) is 46%.                                                      |

| FB1     | 14  | Analog output         | Output for first converter regulation loop.                                                                                                                                                                                         |

| VREF1   | 13  | Analog input          | Reference comparison input for first converter regulation loop. 2.5V.                                                                                                                                                               |

| FB2     | 11  | Analog output         | Output for second converter regulation loop.                                                                                                                                                                                        |

| VREF2   | 12  | Analog input          | Reference comparison input for second converter regulation loop. 2.5V.                                                                                                                                                              |

| RI      | 19  | Program. Analog input | Connected to external resistor for the reference setting.  RI = 75k ohms.                                                                                                                                                           |

| GND     | 15  | Supply                | Ground.                                                                                                                                                                                                                             |

# **BLOCK DIAGRAM**

## **TIMING DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter                                | Value       | Unit       |

|---------------------|------------------------------------------|-------------|------------|

| $V_{CC}$            | DC Supply Voltage at Pin 20              | 16          | V          |

| $V_{FB}$            | Shunt Regulator Output at Fb1, Fb2 Pins  | 16          | V          |

| $I_{OUT}$           | Output Current at PG, Fb1, Fb2 Pins      | 30          | mA         |

| P <sub>D,25°C</sub> | Power Dissipation (T <sub>A</sub> =25°C) | 1.5         | W          |

| P <sub>D,90°C</sub> | Power Dissipation (T <sub>A</sub> =90°C) | 0.5         | W          |

| $T_{STG}$           | Storage Temperature Range                | -55 to +150 | $^{\circ}$ |

| $R_{\theta JA}$     | Thermal Resistance, Junction-To-Air      | 82.5        | °C/W       |

| $T_{J,MAX}$         | Operating Junction Temperature           | 150         | $^{\circ}$ |

| $T_{A,MAX}$         | Operating Ambient Temperature            | -30 to +125 | $^{\circ}$ |

| $T_{\rm L}$         | Lead Temperature (Soldering, 10sec)      | 260         | $^{\circ}$ |

|                     | ESD Capability, HBM model                | 3.0         | kV         |

Note: All voltage values, except differential voltage, are with respect to network ground terminal.

# RECOMMENDED OPERATING CONDITIONS

| Symbol            | Parameter                               | Value      | Unit       |

|-------------------|-----------------------------------------|------------|------------|

| $V_{CC}$          | DC Supply Voltage at Pin 20             | 4.5 to 5.5 | V          |

| $V_{\mathrm{FB}}$ | Shunt Regulator Output at Fb1, Fb2 Pins | 4 to 16    | V          |

| $T_{OPER}$        | Operating Ambient Temperature Range     | -25 to +85 | $^{\circ}$ |

# ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ )

| Symbol                           | Parameter                                   | Test Condition    | Min. | Тур. | Max. | Unit |

|----------------------------------|---------------------------------------------|-------------------|------|------|------|------|

| $I_{CC}$                         | Total Supply Current                        | PG High           | -    | 5    | 10   | mA   |

| $V_{OVP1}$                       | Over-Voltage Protection 3.3 V               | -                 | 3.9  | 4.1  | 4.3  | V    |

| $V_{OVP2}$                       | Over-Voltage Protection 5V                  | -                 | 5.8  | 6.1  | 6.5  | V    |

| $V_{OVP3}$                       | Over-Voltage Protection 12V                 | -                 | 13.9 | 14.5 | 14.9 | V    |

| $V_{UVP1}$                       | Under-Voltage Protection 3.3V               | -                 | 2.0  | 2.6  | 2.8  | V    |

| $V_{UVP2}$                       | Under-Voltage Protection 5V                 | -                 | 3.0  | 3.6  | 3.9  | V    |

| $V_{UVP3}$                       | Under-Voltage Protection 12V                | -                 | 6.0  | 7.2  | 8.0  | V    |

| $V_{\rm UVS1}$                   | Under-Voltage Sense 3.3V for PG Low         | -                 | 2.5  | 2.8  | 3.0  | V    |

| $V_{\mathrm{UVS2}}$              | Under-Voltage Sense 5V for PG Low           | -                 | 4.0  | 4.3  | 4.5  | V    |

| $V_{\rm UVS3}$                   | Under-Voltage Sense 12V for PG Low          | -                 | 9.4  | 10.1 | 10.4 | V    |

| V <sub>OPPS</sub> * <sup>1</sup> | Over-Power Protection.                      | $V_{UVAC} = 1.5V$ | 2.02 | 2.4  | 2.66 | V    |

| $V_{NVP}$                        | Negative Voltage Protection: Voltage Level  | -                 | 2.0  | 2.1  | 2.2  | V    |

| $I_{NVP}$                        | Negative Voltage Protection: Source Current | $RI = 75k\Omega$  | 57   | 64   | 72   | uA   |

| $t_{OVP}$                        | Timing for Over-Voltage Protection          | $RI = 75k\Omega$  | 0.37 | 0.7  | 1.35 | ms   |

| $t_{UVP}$                        | Timing for Under-Voltage Protection         | $RI = 75k\Omega$  | 0.8  | 2.4  | 3.75 | ms   |

| $t_{UVS}$                        | Timing for Under-Voltage Sense for PG Low   | $RI = 75k\Omega$  | 0.37 | 1.2  | 1.88 | ms   |

| t <sub>OPP</sub>                 | Timing for Over-Power-Protection            | $RI = 75k\Omega$  | 3.3  | 7    | 11.3 | ms   |

| t <sub>NVP</sub>                 | Timing for Negative Voltage Protection      | $RI = 75k\Omega$  | 3.3  | 7    | 10.2 | ms   |

Note \*1:  $V_{OPPS} = (2/3) \times V_{OPP} + (1/3) \times V_{UVAC}$ ;

# Shunt Regulator (FB1, VREF1, FB2, VREF2)

| Symbol                  | Parameter                                       | Test Condition                                       | Min.  | Тур. | Max.  | Unit |

|-------------------------|-------------------------------------------------|------------------------------------------------------|-------|------|-------|------|

| $V_{REF}$               | Reference Voltage                               | $I_{FB} = 0.5 \text{ mA}, T_A = 25 ^{\circ}\text{C}$ | 2.475 | 2.5  | 2.525 | V    |

| V <sub>DEV, I</sub> *2  | Deviation of V <sub>REF</sub> Over Load Current | $I_{FB} = 0.5 \text{mA} \text{ to } 10 \text{mA}$    | -     | -    | 20    | mV   |

| V <sub>DEV, T</sub> *2  | Deviation of V <sub>REF</sub> Over Temperature  | $T_A = -25^{\circ}C$ to $85^{\circ}C$                | -     | 10   | 30    | mV   |

| R <sub>EGLI-FB</sub> *2 | Line Regulation                                 | $4 < V_{FB} < 16V$                                   | -     | 1    | -     | mV/V |

| I <sub>OUT-FB</sub> *2  | Output Sinking Current Capability               | $V_{\rm FB} > 2V$                                    | 10    | -    | -     | mA   |

Note \*2: Not tested in production test.

## **Power Good Section**

| Symbol           | Parameter                            | Test Condition         | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------|------------------------|------|------|------|------|

| $t_{PG}$         | Timing for PG Delay                  | $RI = 75k\Omega$       | 200  | 300  | 400  | ms   |

| $V_{UVAC}$       | UVAC Voltage Sense for PG            | -                      | 0.65 | 0.7  | 0.75 | V    |

| $t_R^{*2}$       | PG Good Output Rising Time           | $C_L = 100 pF$         | -    | 1    | -    | us   |

| $t_F^{*2}$       | PG Good Falling Time                 | $C_L = 100 pF$         | -    | 300  | -    | ns   |

| $V_{OL2}$        | Power Good Output Saturation Level   | $I_{PG} = 5 \text{mA}$ | -    | -    | 0.5  | V    |

| I <sub>ON2</sub> | Power Good Leakage Current Collector | $V_{PG} = 5V$          | -    | -    | 1    | uA   |

## Remote On/Off

| Symbol                 | Parameter                    | Test Condition   | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------|------------------|------|------|------|------|

| V <sub>PSON</sub>      | PSON Input Threshold Level   | -                | 1    | 1.4  | 2.0  | V    |

| I <sub>PSON</sub>      | Remote Input Driving Current | -                | -    | -    | 0.5  | mA   |

|                        | Timing PSON to On/Off        |                  |      |      |      |      |

| t <sub>PSON(ON)</sub>  | On                           | $RI = 75k\Omega$ | 17   | 26   | 45   | ms   |

| t <sub>PSON(OFF)</sub> | Off (PS-off)                 |                  | 5    | 7.5  | 28.8 |      |

| t <sub>PSOFF</sub>     | Timing PG low to Power Off   | $RI = 75k\Omega$ | 1.5  | 2    | 6.3  | ms   |

# **Error Amplifier**

| Symbol              | Parameter                    | Test Condition | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------|----------------|------|------|------|------|

| $V_{2.5}$           | Reference Voltage            | -              | 2.45 | 2.5  | 2.55 | V    |

| ${\rm I_{IB}}^{*2}$ | Input Bias Current           | -              | -    | -    | 0.1  | uA   |

| A <sub>VOL</sub> *2 | Open-Loop Voltage Gain       | -              | 50   | 60   | -    | dB   |

| BW * 2              | Unity Gain Bandwidth         | -              | 0.3  | 1    | -    | MHz  |

| PSRR *2             | Power Supply Rejection Ratio | -              | 50   | -    | -    | dB   |

## **Oscillator Section**

| Symbol | Parameter     | Test Condition   | Min. | Тур. | Max. | Unit |

|--------|---------------|------------------|------|------|------|------|

| Fosc   | PWM Frequency | $RI = 75k\Omega$ | 60   | 65   | 70   | KHz  |

## **Soft-Start Section**

| Symbol   | Parameter      | Test Condition   | Min. | Тур. | Max. | Unit |

|----------|----------------|------------------|------|------|------|------|

| $I_{SS}$ | Charge Current | $RI = 75k\Omega$ | 6    | 8    | 9.3  | uA   |

SG6105

# **Comparator Section**

| Symbol | Parameter  | Test Condition | Min. | Тур. | Max. | Unit |

|--------|------------|----------------|------|------|------|------|

| DC     | Duty Cycle |                | 85   | -    | 93   | %    |

# **PWM Output Section (OP1, OP2)**

| Symbol         | Parameter                           | Test Condition | Min. | Тур. | Max. | Unit |

|----------------|-------------------------------------|----------------|------|------|------|------|

| $V_{OL}$       | Output Voltage Low                  | Io = 5mA       | -    | -    | 0.5  | V    |

| $V_{OH}$       | Output Voltage High                 | V12 = 12V      | 4    | -    | -    | V    |

| R <sub>O</sub> | Output Impedance of V <sub>OH</sub> | -              | 1.5  | -    | 3.3  | kΩ   |

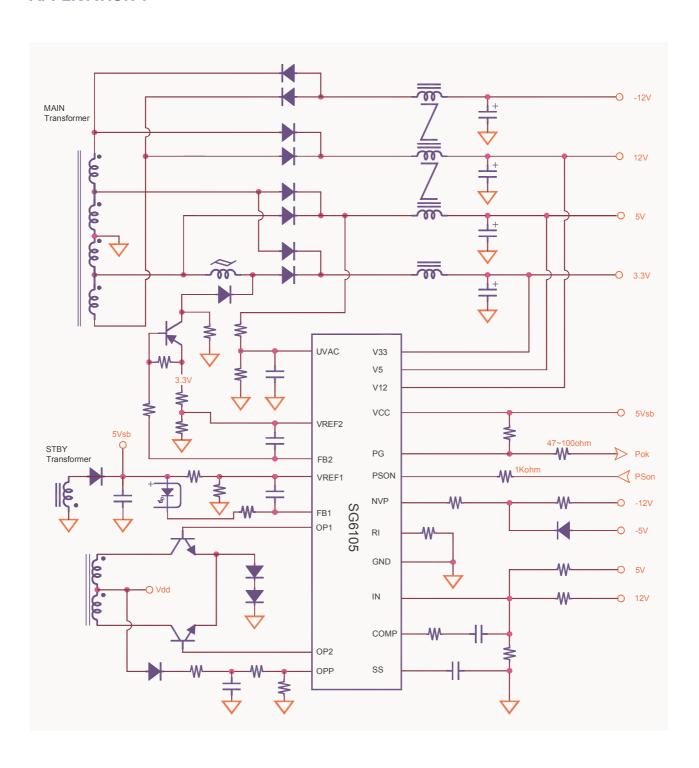

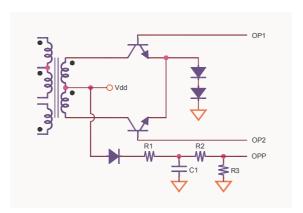

# **APPLICATION 1**

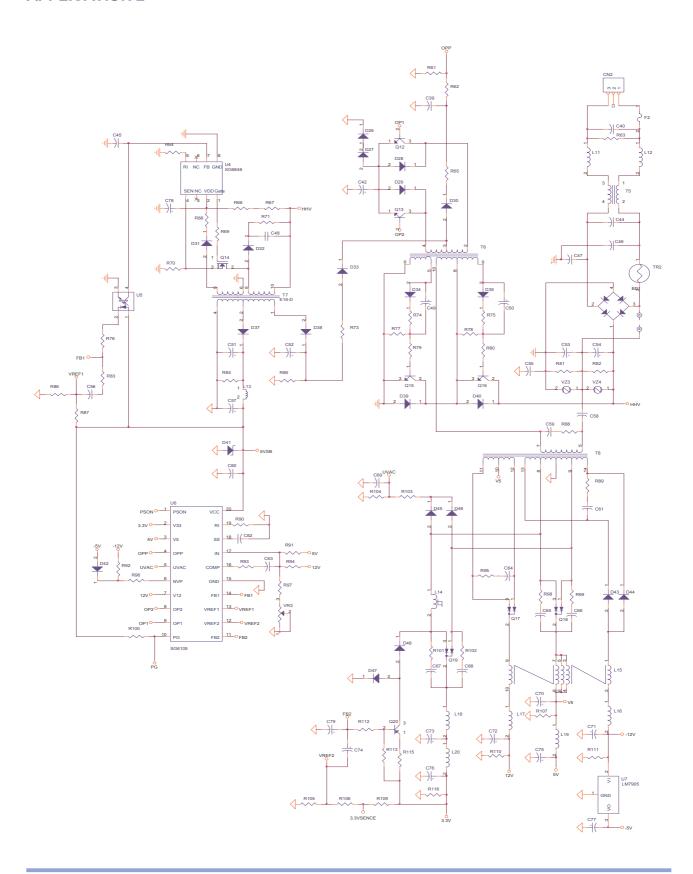

# **APPLICATION 2**

# **Example of Using SG6105 for the ATX Power Supply**

Protection against over-voltage, short-circuit and fault conditions is mandatory in PC power supplies. These protection circuits can be realized by using many discrete components and comparators, which occupy a lot of PCB space and also add to assembling costs. This single chip controller IC provides complete protection circuits, shunt regulators, and PWM control function and with less number of components. SG6105 is an ideal controller IC for PC switching mode power supplies.

The features and benefits of this device are listed below:

- Over-voltage and under-voltage protection for 3.3V,

5V and 12V without external divider

- Over-power protection.

- UV protection for -12V and/or -5V.

- Power-down warning for power good signal.

- Power good signal and power-fail lockup

- Remote on/off control.

- Delay time for PSON and PS-off signal.

- Two shunt regulator for 3.3V and 5V-Standby regulation.

- Complete pulse width modulation (PWM) control circuitry.

- On-chip oscillator.

- Programmable Soft-Start.

- Maximum 93% duty cycle

- Few external components

- More reliable system

- Little space on PCB

- Easy trouble-shooting and implementation

### **FEATURE DESCRIPTIONS**

- Over voltage protection can be implemented without any additional components. Over-voltage sense Levels or 3.3V, 5V, 12V are 4.1V, 6.1V, 14.5V respectively.

- Over current and/or short circuit protection can also be achieved by using over-power protection, in which OPP pin is connected to the current transformer (driver transformer).

- The power good signal is asserted to indicate the 3.3V, 5V and 12V is above the under voltage

threshold level. PG pin goes high when the above condition is reached. A 2K pull up resistor may connect to 5V.

- The VCC can be supplied from the 5V-standby. When the VCC voltage is higher than 7V, besides the shunt regulator, the circuit of SG6105 will be shutdown and reset. No extra power supply is needed.

- Two internal high precision 431 shunt regulators are built-in. It provides stable reference voltages.

- Complete PWM control circuitry including the error amplifier for push-pull or half-bridge operation.

## **Supervisory Circuit Operation**

The PC generates the remote ON/OFF logic (PSON), which is "Low" for power supply "On" and "High" to switch off the power supply. The remote ON/OFF is connected to PSON input.

#### **APPLICATION GUIDES**

#### Introduction

The application guide shows the key-feature of SG6105 and illustrates how to use in an ATX switching mode power supply (SMPS). SG6105 is suitable for half-bridge, push-pull topology. It incorporates with a 4-channel supervisor, including 5V-standby. The PWM section of SG6105 comprises a built-in 65kHz oscillator and high immunity circuits, which protect the system from noise interference and provide more noise margins for improper PCB layout. SG6105 has OVP and UVP for 12V, 5V and 3.3V. Besides, the NVP is used for negative voltage protection, such as –12V and/or –5V. The UVAC (AC fails detection) is applied to detect AC line condition. Two built-in internal precision TL431 shunt regulators can be used for 3.3V or 5V auxiliary standby power.

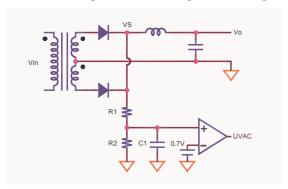

#### **AC Fails Detection**

Through a resistor divider, UVAC is connected to the secondary power transformer for detecting the AC line condition. Once the voltage of UVAC is lower than 0.7V for a period of time, such as 200usec, the PG (power good) signal will be pulled low to indicate an AC line power-down condition. The voltage amplitude of the

PWM switching signal in the secondary power transformer is proportional to the AC line voltage. Adjust the ratio of resistor divider to decide the threshold of power-down warning. A small capacitor is connected from UVAC to ground for filtering the switching noise.

## **Over Power Protection (OPP)**

The OPP (over power protection) is used for detecting over power and/or short-circuit conditions. When OPPS voltage (p.4, Note-1) is higher than 2.1V and this situation existed for longer than 7 msec, 6105 will pull the PG low and lock off the power outputs.

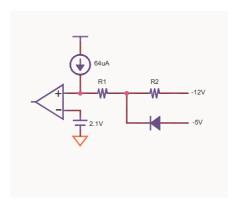

## **Negative Voltage Protection**

The NVP provides an UVP (under voltage protection) for negative voltage outputs. An under-voltage represents the phenomenal of the overload condition in negative voltage output. For example, the -12V output may drop to -10V during the overload situation. A resistor determining the threshold of the protection is connected from pin NVP to the negative voltage output. Via this resistor, NVP outputs a 64uA constant current to the negative voltage output. When the NVP voltage is over 2.1V and the situation kept for longer than 7 msec, 6105 will lock the power outputs off.

$$VNVP = 64 \text{ uA} \times (R1 + R2) - V-12V$$

The power outputs will be locked off when  $VNVP \ge 2.1V$ .

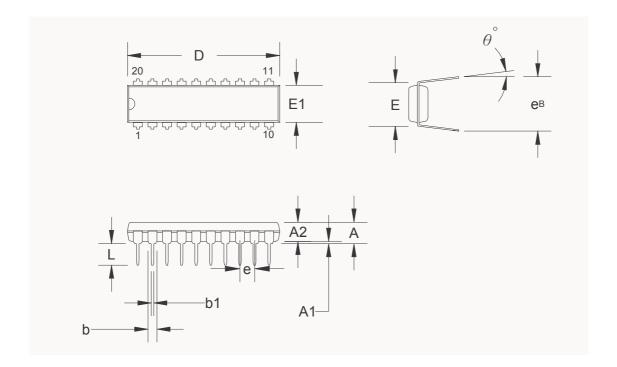

# MECHANICAL DIMENSIONS 20 PINS - DIP (D)

## **Dimension**

| Symbol | Millimeter |        |        | Inch  |       |       |  |

|--------|------------|--------|--------|-------|-------|-------|--|

|        | Min.       | Typ.   | Max.   | Min.  | Тур.  | Max.  |  |

| A      |            |        | 5.334  |       |       | 0.210 |  |

| A1     | 0.381      |        |        | 0.015 |       |       |  |

| A2     | 3.175      | 3.302  | 3.429  | 0.125 | 0.130 | 0.135 |  |

| b      |            | 1.524  |        |       | 0.060 |       |  |

| b1     |            | 0.457  |        |       | 0.018 |       |  |

| D      | 24.892     | 26.162 | 26.924 | 0.980 | 1.030 | 1.060 |  |

| Е      |            | 7.620  |        |       | 0.300 |       |  |

| E1     | 6.223      | 6.350  | 6.477  | 0.245 | 0.250 | 0.255 |  |

| e      |            | 2.540  |        |       | 0.100 |       |  |

| L      | 2.921      | 3.302  | 3.810  | 0.115 | 0.130 | 0.150 |  |

| $e_B$  | 8.509      | 9.017  | 9.525  | 0.335 | 0.355 | 0.375 |  |

| θ°     | 0°         | 7°     | 15°    | 0°    | 7°    | 15°   |  |

### **DISCLAIMERS**

#### LIFE SUPPORT

System General's products are not designed to be used as components in devices intended to support or sustain human life. Use of System General's products in components intended for surgical implant into the body, or other applications in which failure of the System General's products could create a situation where personal death or injury may occur, is not authorized without the express written approval of System General's Chief Executive Officer. System General will not be held liable for any damages or claims resulting from the use of its products in medical applications.

#### **MILITARY**

System General's products are not designed for use in military applications. Use of System General's products in military applications is not authorized without the express written approval of System General's Chief Executive Officer. System General will not be held liable for any damages or claims resulting from the use of its products in military applications.

#### **RIGHT TO MAKE CHANGES**

System General reserves the right to change this document and/or this product without notice. Customers are advised to consult their System General sales representative before ordering.