# SERVICE MANUAL

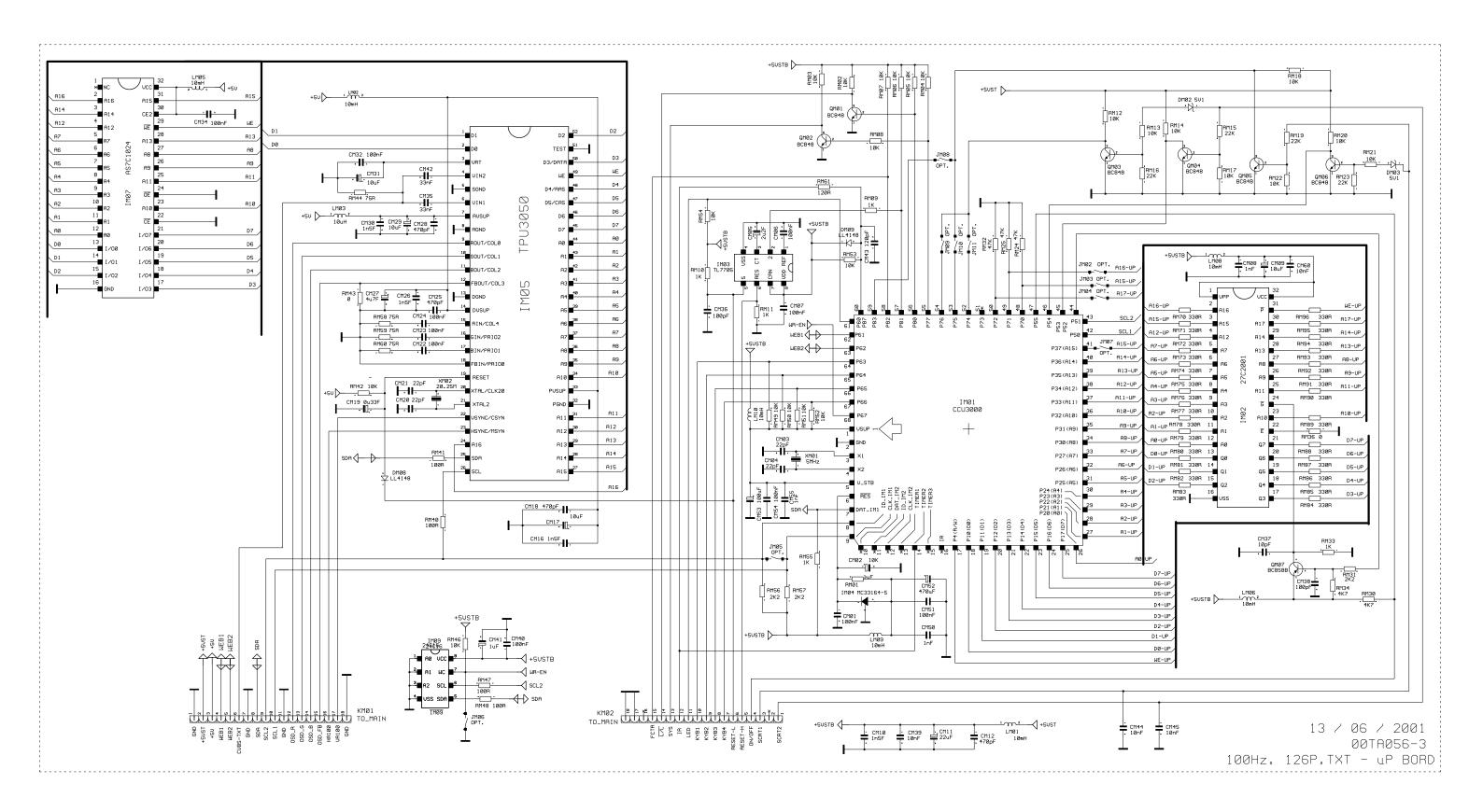

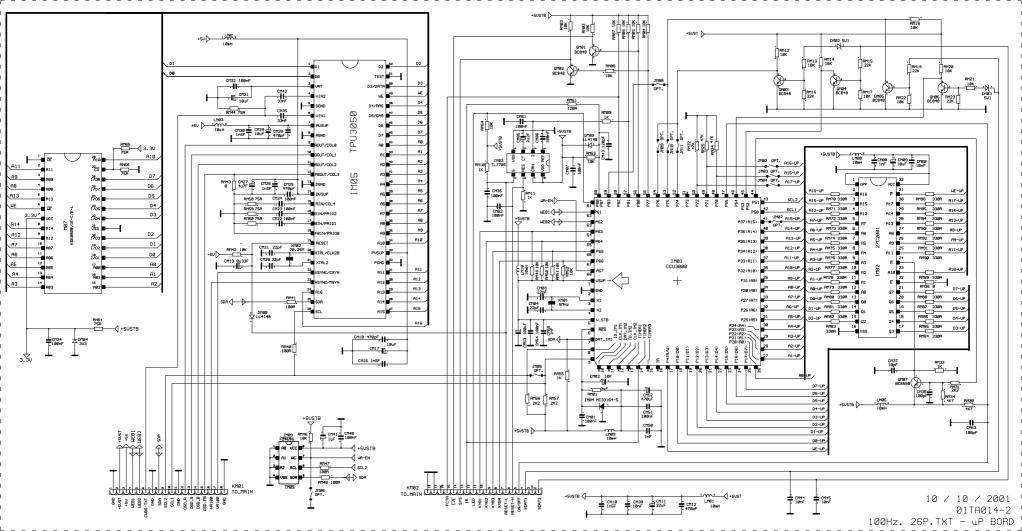

# 100 Hz Chassis 28" CTV

# Contents

| Technical Data          |                                            |

|-------------------------|--------------------------------------------|

| Recommendation for      | service repairs5                           |

| Component description   | 7                                          |

| Scart pin descriptions  |                                            |

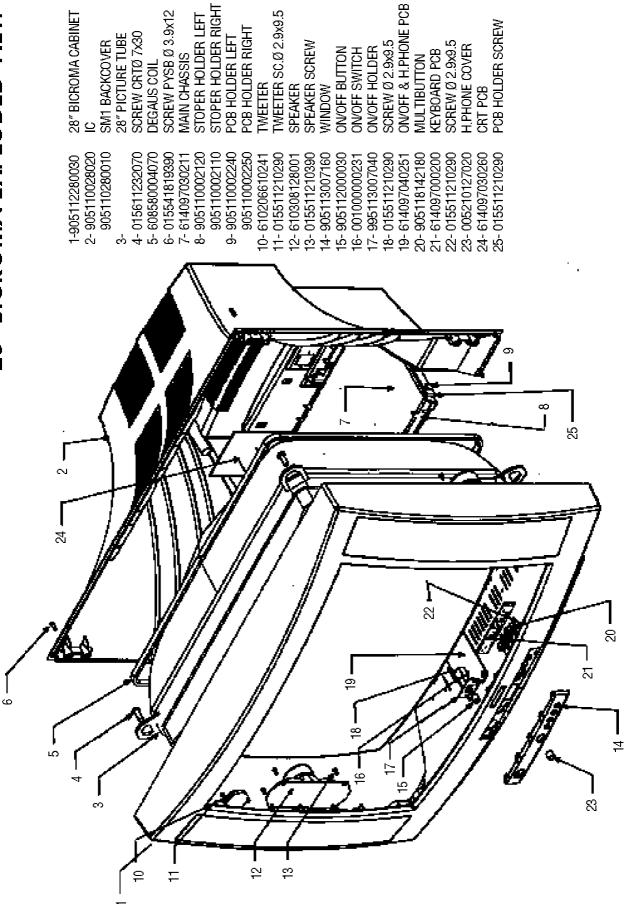

| Exploded views          |                                            |

| Specifications of the c | onnector                                   |

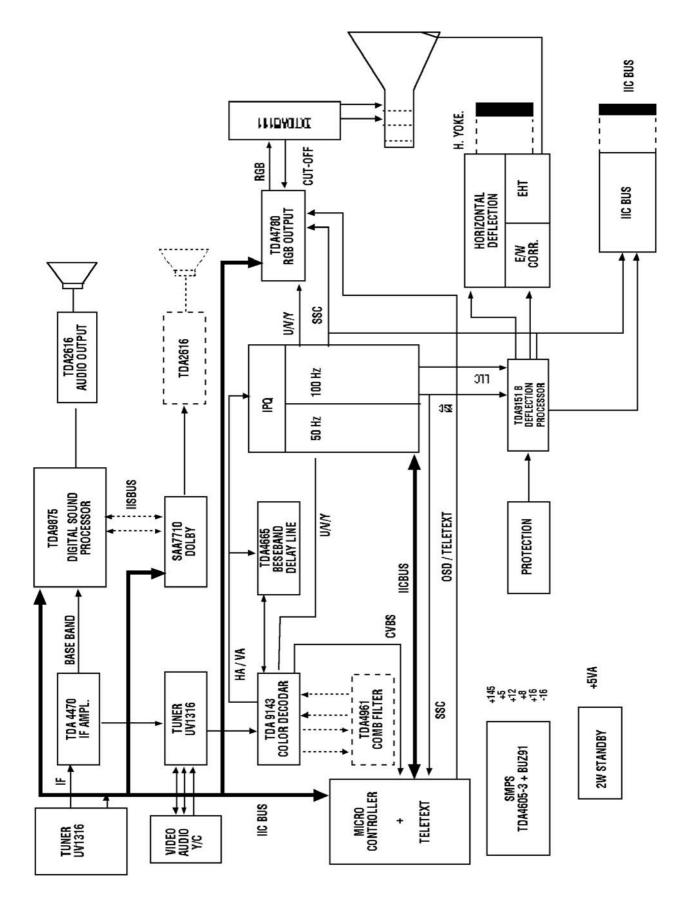

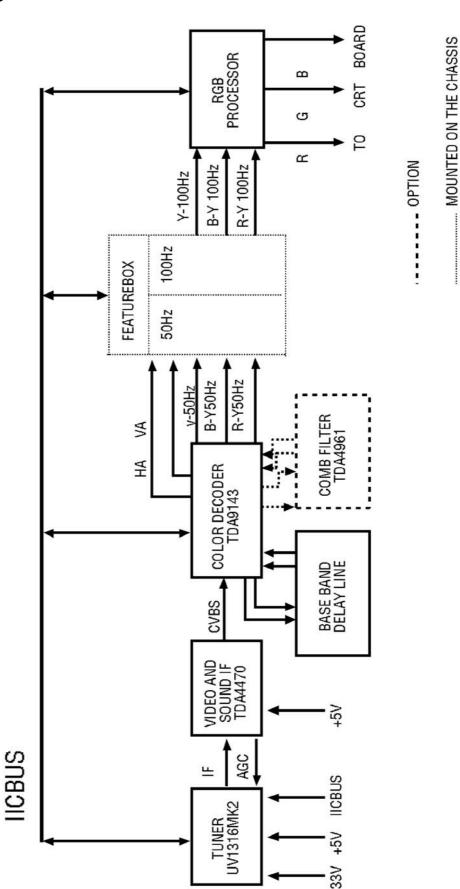

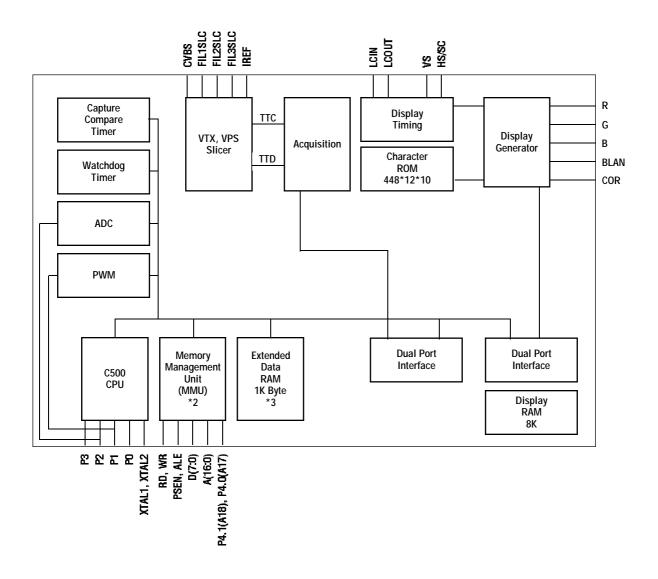

| Block diagram           |                                            |

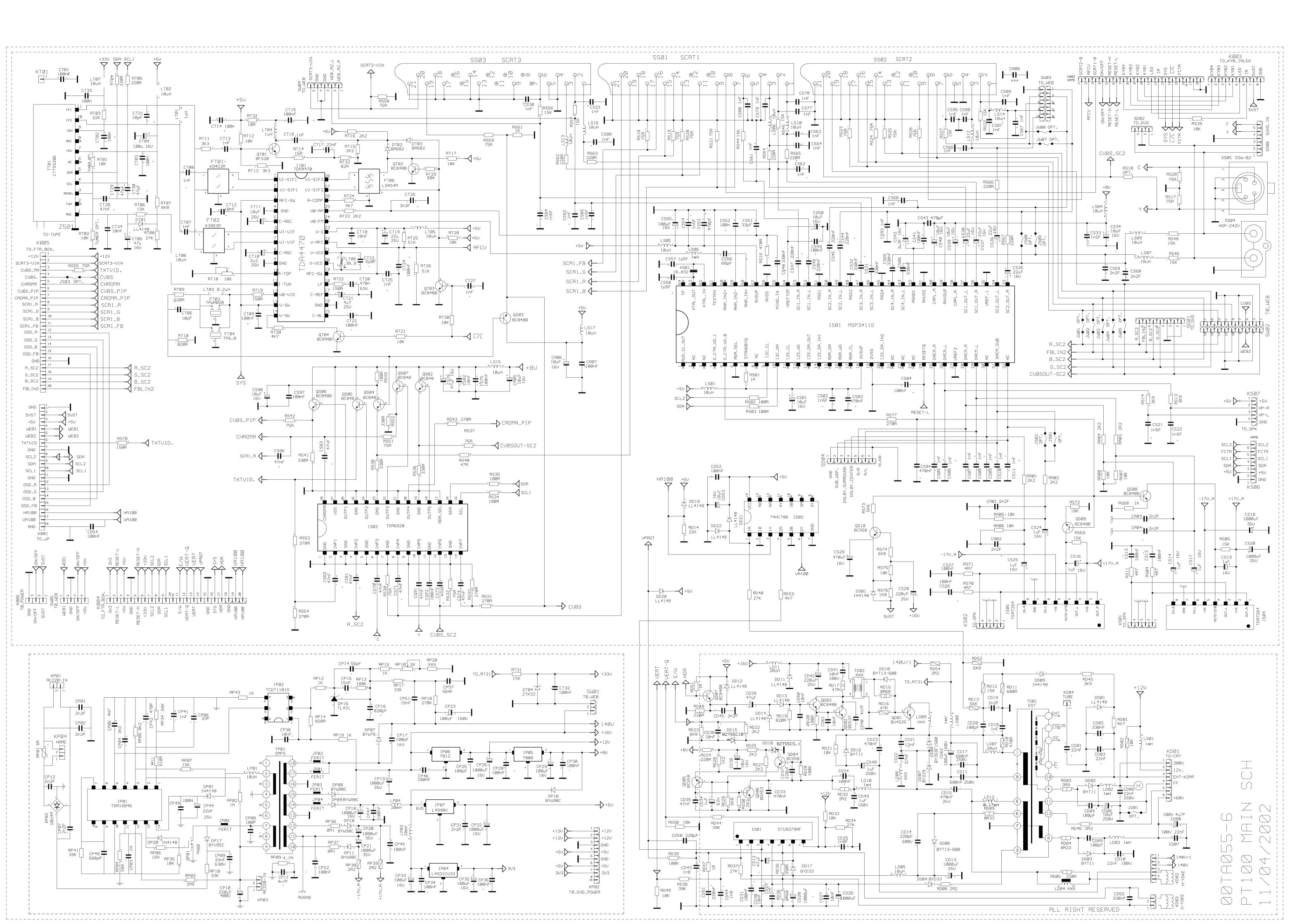

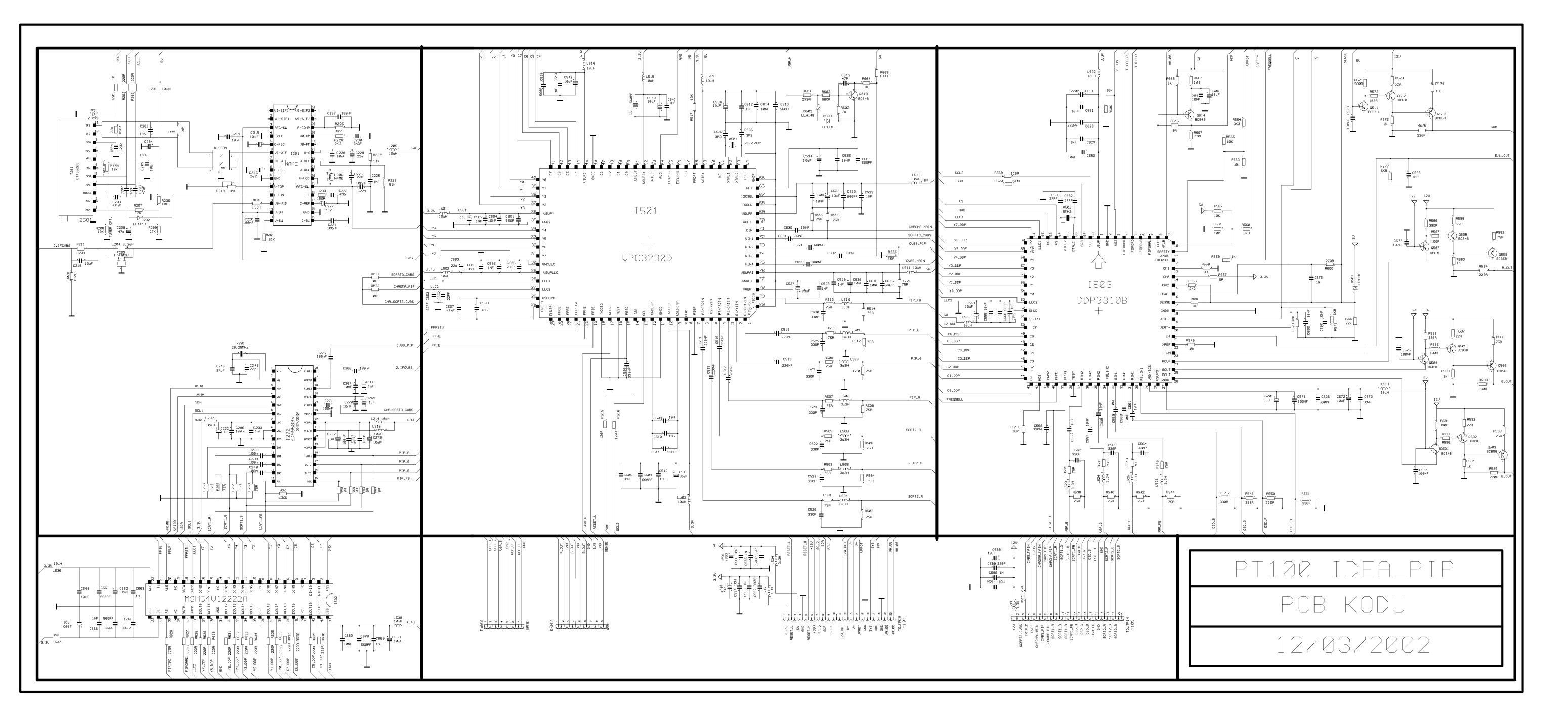

| Video - Board           |                                            |

| Circuit Description     |                                            |

| Component Description   | 2ns                                        |

| TDA4780                 | (RGB video processor)                      |

| TDA4665                 | (Base band delay - line)                   |

| TDA9143                 | ( <i>PC-Bus Controlled</i> )               |

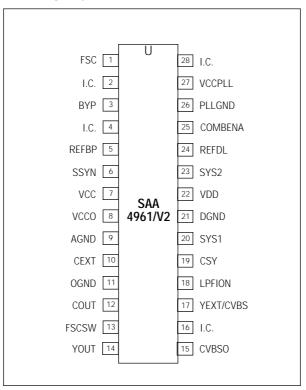

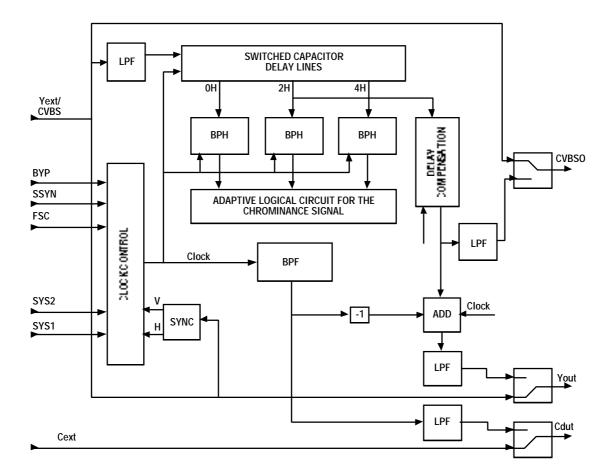

| SAA4961                 | (Multistandard Comb Filter)                |

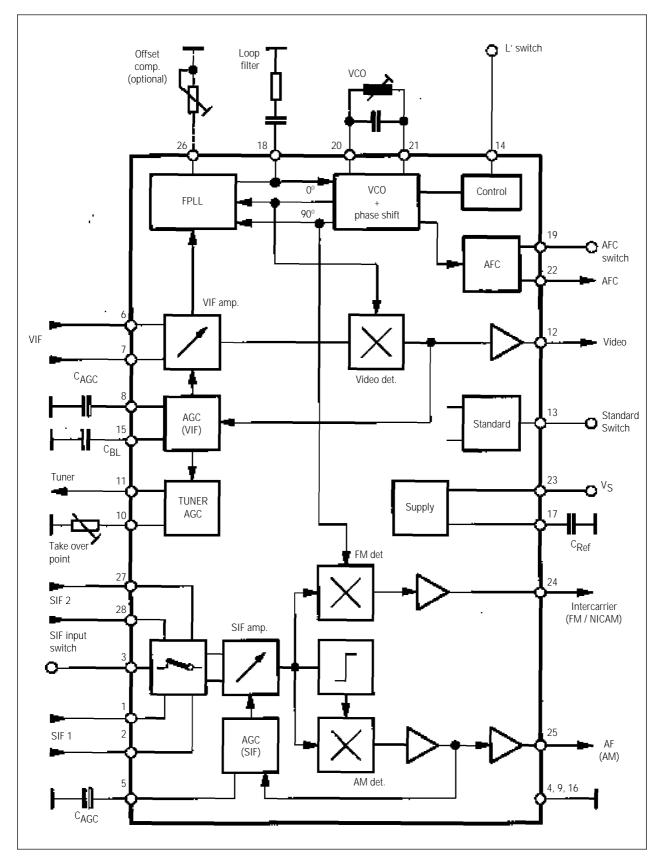

| TDA4470B                | (Multistandard video -                     |

|                         | IF and quasi parallel sand processing)     |

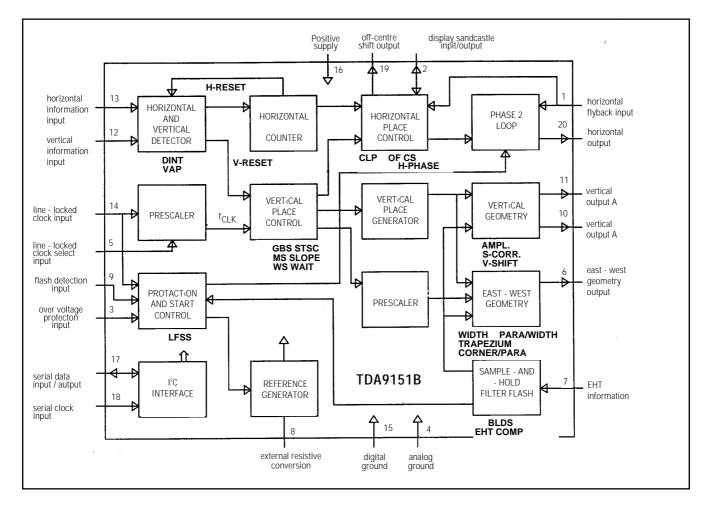

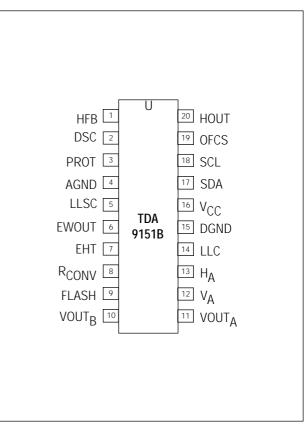

| TDA9151B                | (Programmable deflection controller)40     |

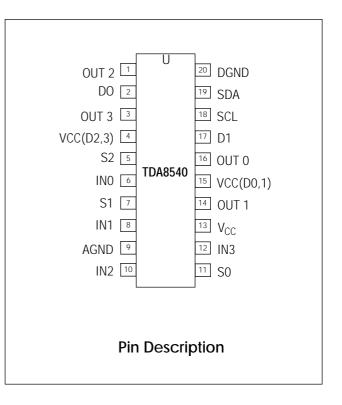

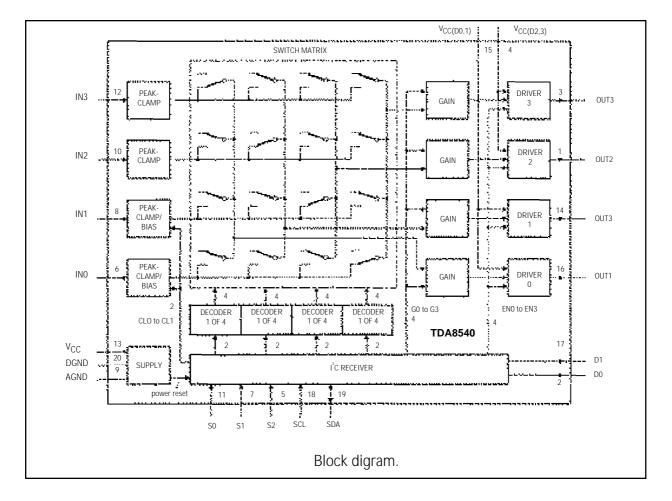

| TDA8540                 | (4x4 video switch matrix)                  |

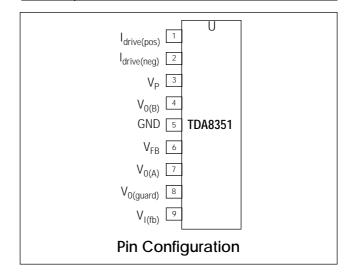

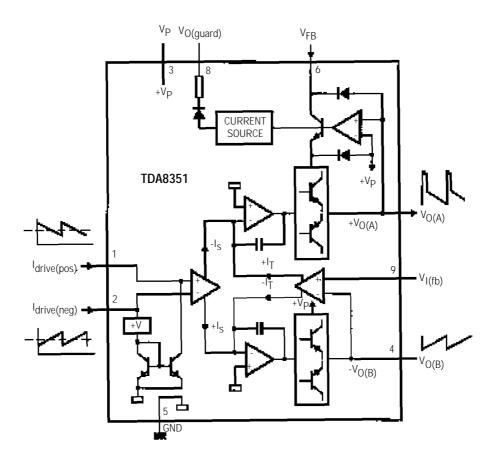

| TDA8351                 | (DC-coupled vertical deflection circuit)48 |

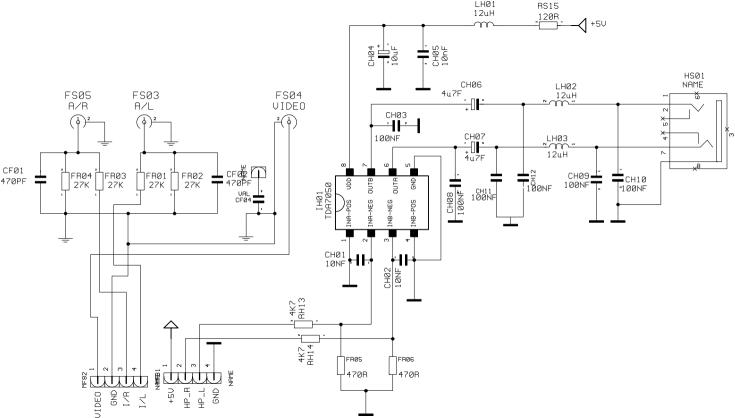

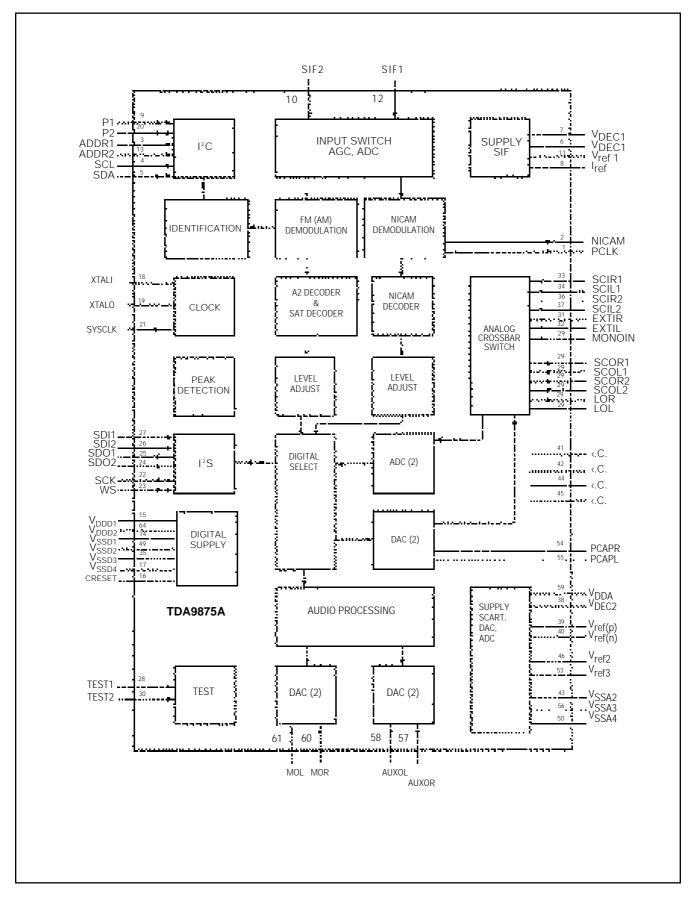

| TDA9875A                | (Digital TV sound processor)               |

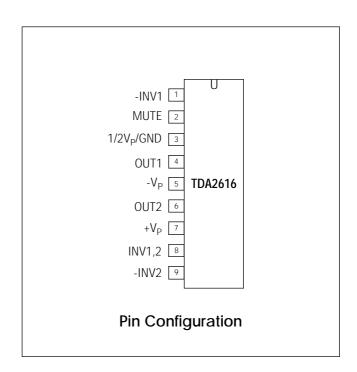

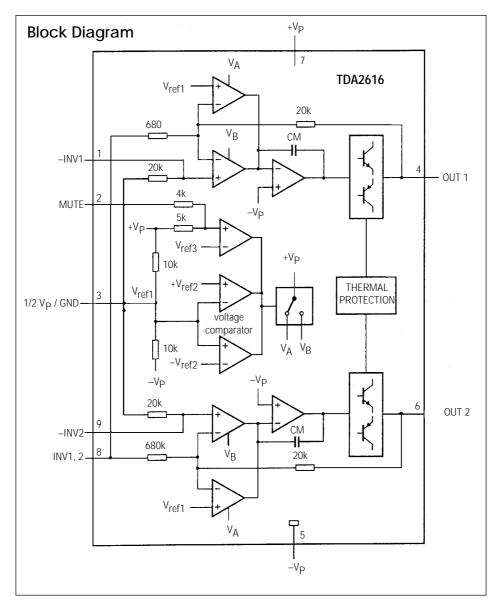

| TDA2616                 | (2x12W Hi-Fi audio power)57                |

| TDA4605                 | (Control IC for SMPS)                      |

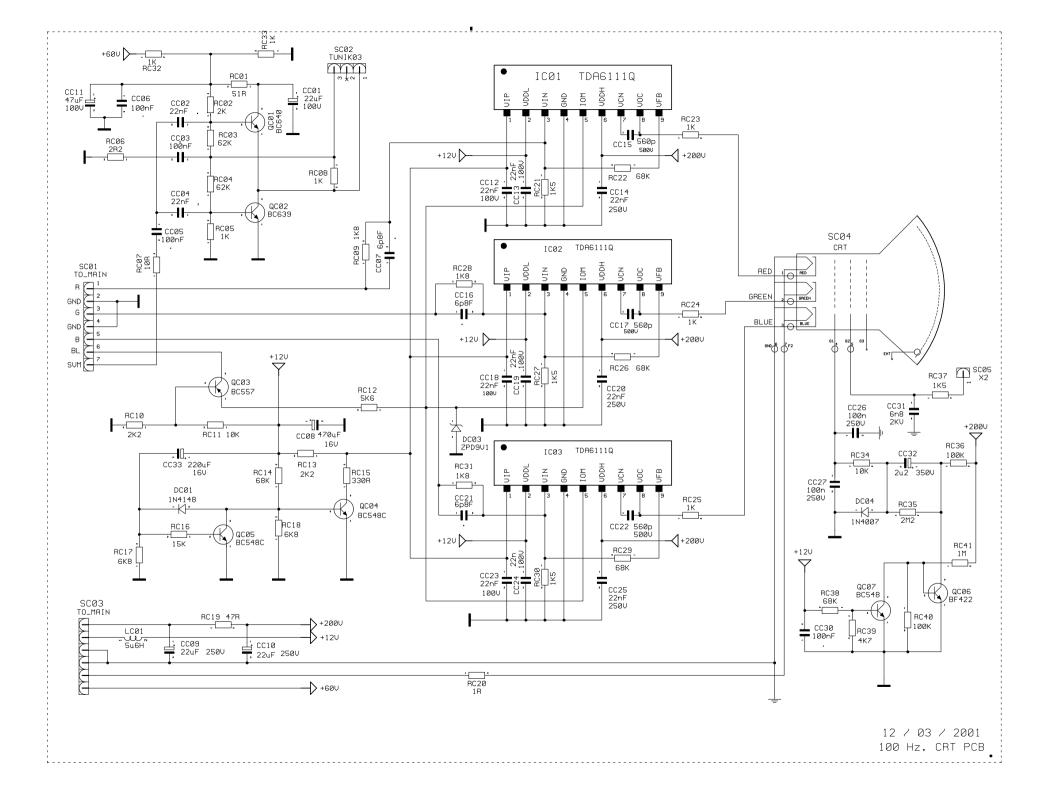

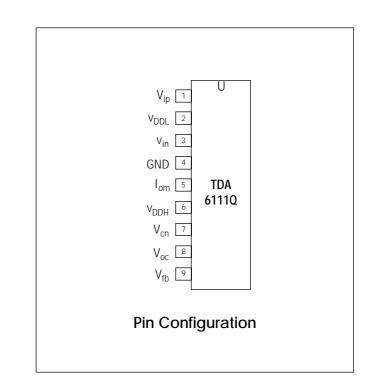

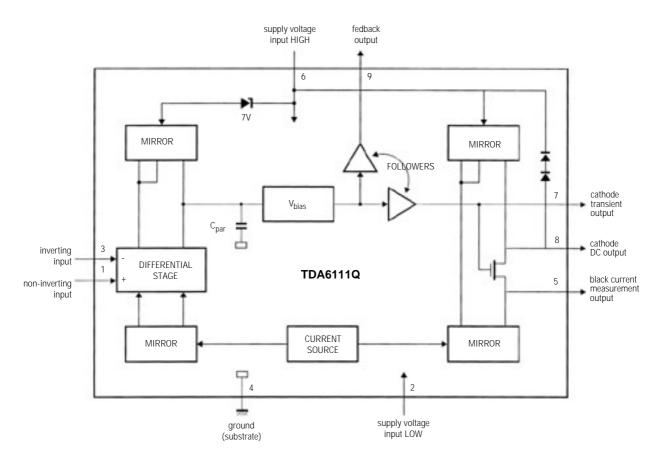

| TDA6111Q                | (Video output amplifier)                   |

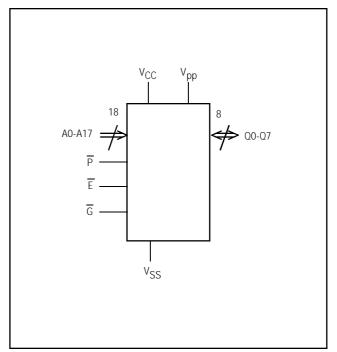

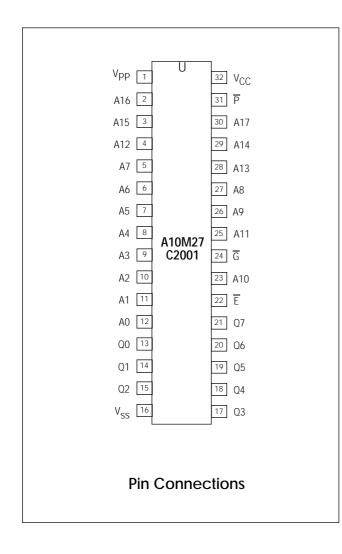

| M27C2001                | (2 megabit UV eprom)                       |

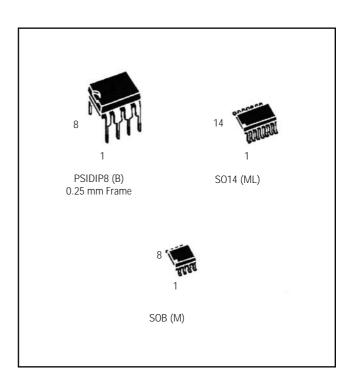

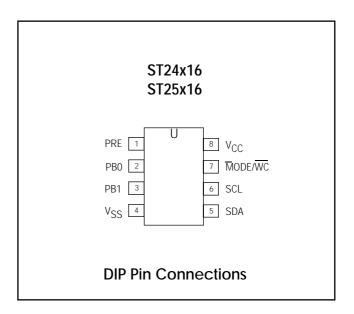

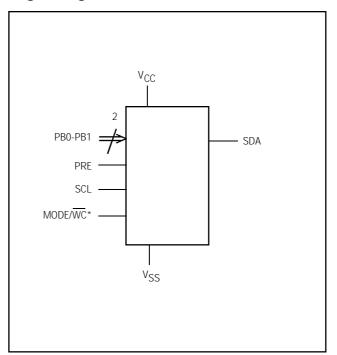

| ST24C16                 | (Serial 16K eeprom)                        |

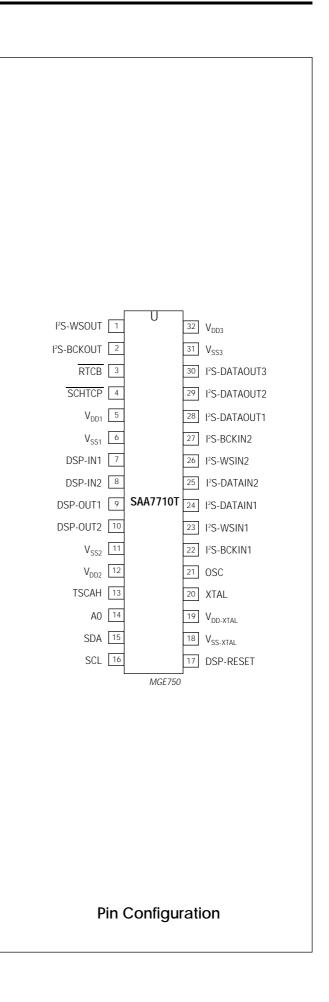

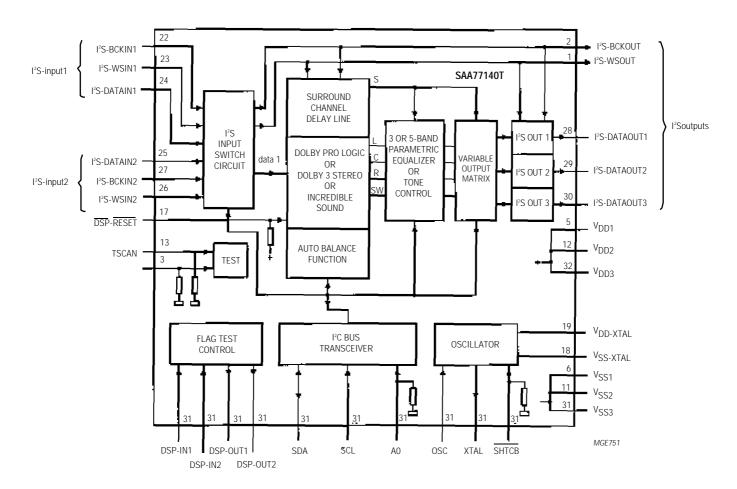

| SAA7710                 | (Dolby Pro Logic Surround)                 |

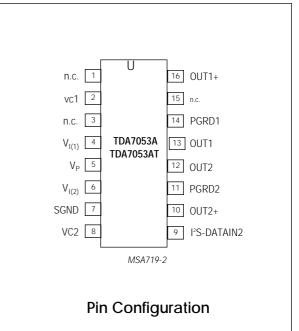

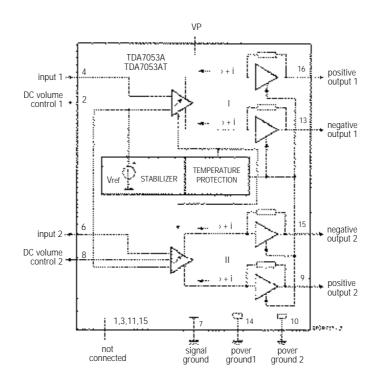

| SAA7053A                | (Stereo BTL audio output)                  |

| SDA5250                 | (Microcontroller unit)                     |

| Oscilloscope signals    |                                            |

|                         |                                            |

# **TECHNICAL DATA**

| CRT PANEL            |          |

|----------------------|----------|

| Visible Picture      | 66 cm    |

| Deflection Angle     | 110°     |

| Vertical Frequency   | 100Hz    |

| Horizontal Frequency | 31.250Hz |

### ELECTRONIC

| Program Number | 100+2AV +SVHS                         |

|----------------|---------------------------------------|

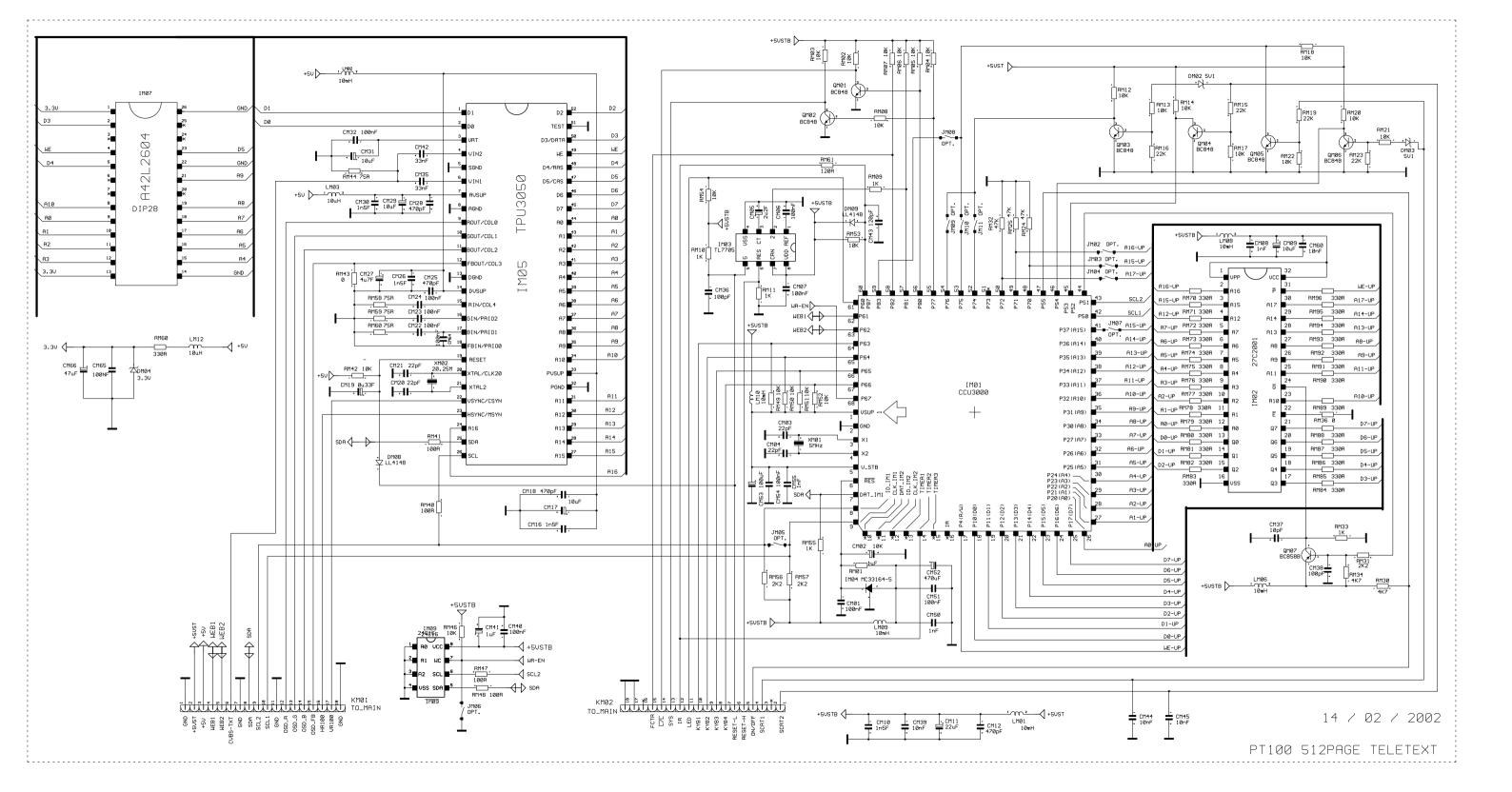

| Teletext       | 8 pages fast text (Top text optional) |

| Tuner          | PLL                                   |

| TV System      | European CCIR system                  |

| Music Power    | 2x8Watt Rms 10% distortion            |

#### CONNECTIONS

| Euro AV Socket | Include |

|----------------|---------|

| SVHS           | Include |

### MAIN STAGE

|                   | <u> </u>   |

|-------------------|------------|

| Mains Voltage     | 165-260VAC |

| Mains Frequency   | 50Hz       |

| Power Consumption | 145W       |

| In Stby Mode      | 2W         |

# **RECOMMENDATION FOR SERVICE REPAIRS**

- 1- Use only original spare parts. Only use components with the same specifications for replacement.

- 2- Original fuse value only should be used.

- 3- Main leads and connecting leads should be checked for external damage before connection.

Check the insulation.

Parts contributing to the safety of the product must not be damaged or obviously unsuitable.

This is valid especially for insulators and insulating parts.

- 5- Thermally loaded solder pads are to be sucked off and re-soldered.

- 6- Ensure that the ventilation slots are not obstructed.

- 7- Potentials as high as 31 KV are present when this receiver is operating. Operation of the receiver outside the cabinet or with back cover removed involve a shock hazard from the receiver.

Servicing should not be attempted by anyone who is not thoroughly familiar with the precautions necessary when working on high voltage equipment.

Perfectly discharge the high potential of the picture tube before handling the tube. The picture tube is highly evacuated and if broken.

Glass fragments will be violently expelled.

Always discharge the picture tube anode to the receiver chassis to keep of the shock hazard before removing the anode cap.

- 8- Keep wire away from the high voltage or high temperature components.

- 9- When replacing a wattage resistor in circuit board, keep the resistor 10 mm away from circuit board.

- 10) Discharging of the picture tube is effected only by the connection point of the aquadaq coating the picture tube.

- 11) When carrying out repairing process at control unit do not approach too near to the picture tube in order to avoid any charge transfer.

- 12) Measurements within the primary circuit of the switched mode power supply are allowed to be carried out only when using potential-free measuring equipment. Voltages indicated for this circuit are based on mains voltage reference level.

- 13) The defined local radiation dosage according to the x-ray radiation regulation is given by the specific type of the picture tube and the maximum permissible EHT voltage. The EHT voltage must not exceed the maximum value of 31kv.

- 14) When the repair process is carried out 12 V line voltage should not be interrupted because video output stage is endangered by the interruption of 12 V line voltage.

# HANDLING OF MOS CHIP COMPONENTS

MOS circuit requires special attention with regard to static charges. Static charges may occur with any highly insulating plastics and can be transferred to persons wearing clothes and shoes made of synthetic materials. Protective circuits on the inputs and outputs of mos circuits give protection to a limited extend only due to time of reaction.

Please observe the following instructions to protect the components against damage from static charges.

1- Keep mos components in conductive packa-

ge until they are used. Most components must never be stored in styropor materials or plastic magazines.

- 2- Persons have to rid themselves of electrostatic charges by touching MOS components.

- 3- Hold the component by the body touching the terminals.

- 4- Use only grounded instruments for testing and processing purposes.

- 5- Remove or connect MOS ICs when operating voltage is disconnected.

# **X-RAY RADIATION PRECAUTION**

1- Excessive high voltage can be produce potentially hazardous X-RAY radiation. To avoid such hazard, the high voltage must not be above the specified limit. The value of the high voltage of this receiver is 30KV at zero beam current (minimum brightness) under 220V AC power source. The high voltage must not under any circumstance, exceed 31.5KV. It is recommended the reading of the high voltage be recor-

SOLDERING PROCESS

# 1) SMD Components (Surface Mounted Device)

#### **Desoldering:**

Heat up the component from its terminals for 2 or 3 seconds with a soldering iron and afterwards take out the component carefully by means of the tweezers. Remove superfluous solder at the solder surfaces of the components place at pcb by means of desoldering strand or suction de-solder equipment. Never force the component for removing without heating the terminals sufficiently. Unsoldered components should not be used for once more.

#### Soldering:

Place the component properly to its position by means of tweezers and solder one side of the component. Then check out the position of the component and be sure if it is soldered to the right place and then solder other side of the ded as a part of the service record. It is important to use an accurate and reliable high voltage meter.

2- The primary source of X-RAY radiation in this TV receiver is the picture tube. For continued X-RAY radiation protection, the replacement tube must be exactly the same type tube as specified in the part list.

component. Terminals of the SMD components must not contact directly to the soldering iron.

### 2)PLCC Components

#### **Desoldering:**

Heat up the terminals of PLCC component for 3 or 5 seconds by means of SMD soldering iron and PLCC desoldering pair (angle 90°C, Leg: 24mm). Take out PLCC component carefully by slightly turning of desoldering tweezers.

#### Soldering:

Remove superfluous solder at the solder surfaces of the components placed on pcb by means of de-soldering iron or suction de-solder equipment. Apply flux with low grease content. Place PLCC device on the soldering surface and take care for its correct placement. Secure diagonally by means of two soldering joints. Apply soldering paste along PLCC pins. Short circuits which may occure during soldering process have to be removed immediately with a soldering iron.

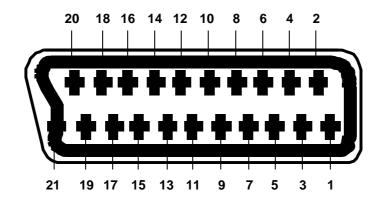

# SPECIFICATIONS OF THE CONNECTOR (EURO SCART)

- I- Audio output 1. right channel 0.5 VRMS/<1 k 0

- 2- Audio input 1. right channel 0.5 VRMS (connected to No.6)

- 3- Audio output 2. left channel 0.5 VRMS (connected to No.1)

- 4- GND (audio)

- 5- GND

- 6- Audio input 2. left channel 0.5 VRMS/>10k 0

- 7- RGB input, blue (B)

- 8- Switch signal video (status)

- 9- GND

- 10- Reserved for clock signals (not connected)

- 11- RGB input, green (G)

- 12- Reserved for remote control (not connected)

- 13- GND

- 14- GND switch signal RGB

- 15- RGB input, red (R)

- 16- Switch signal RGB

- 17- GND (video)

- 18- GND

- 19- Video output 1 Vpp/75 ohm

- 20- Video input 1 Vpp/75 ohm

- 21- Shield

# **BLOCK DIAGRAM**

# **VIDEO BOARD**

# **CIRCUIT DESCRIPTION**

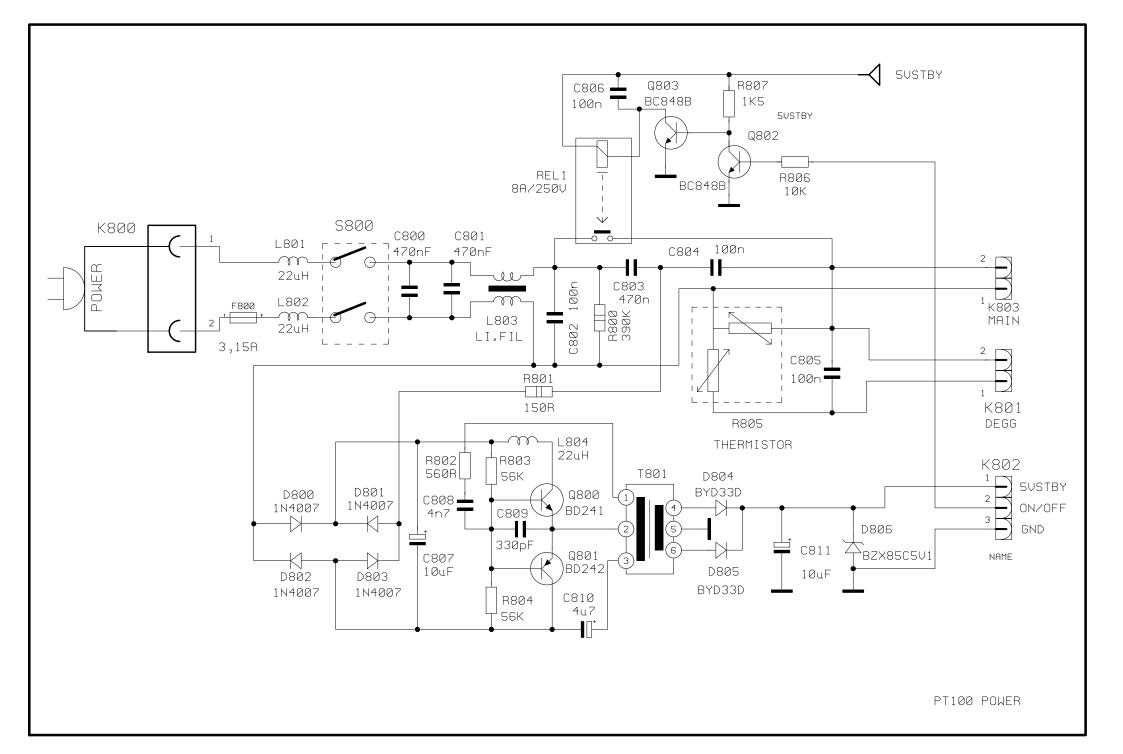

# **1- MAIN SUPPLY UNIT**

### **A-General Description**

In order to obtain 2W power at standby mode, two separate circuits are used. One for standby power supply and another for switched-mode power supply.

The standby supply unit consists of a push-pull converter (Q803 and Q804) producing the required 5V operating voltage by full wave rectification. This voltage is stabilised by means of D807 and D808. This voltage runs the  $\mu$ P (SDA 5250) and IR receiver.

When the standby unit is operating, the under-current relay is pulled up and capacitor C806 which acts as a capacitive series resistor becomes parallel to C807 providing an additional current flow.

To assure the EMC this mains voltage is filtered by multiple choking the feed lines. During standby state the main switched-mode power supply and the degaussing coil are fully disabled by under-current relay. Switching back into the operating state is enabled by the starting-up voltage coming from  $\mu p$  (1701).

The main switched-mode power supply unit including a fly back converter controlled by an optoelectronic coupler consists the driving IC TDA 4605-3 and the switching transistor BUZ91. The following operating voltages are delivered by the transformer of the switched-mode power supply after their rectification.

| 145Vdc | : +B Line is a direct output voltage | ١. |

|--------|--------------------------------------|----|

|--------|--------------------------------------|----|

- 33VDC : +F Delivered from 145vdc

- +16Vdc : +H Horizontal driver voltage.

- +12Vdc : +I Derived from +H Supply of the CRT board and the protection circuit.

- +8Vdc : +C Delivered from +I. Supply of the deflection processor, switched matrix, RGB decoder etc.

- +5Vdc : +D (digital 5v). Supply of the digital part of feature box, μP, DSP (digital sound processor) etc.

- +5Vdc : +A Supply of the analog part of feature box, μP, DSP (digital sound processor) headphone amplifier etc.

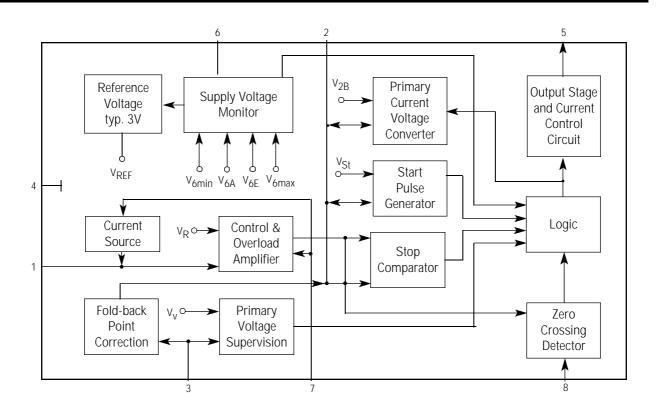

### B-Pin Descriptions of the TDA4605-3

| PIN 1  | Control input signal by comparing the control voltage across control winding 7-9 (SMPS) with an internal re-<br>ference voltage, the width of the output pulse at pin 5 of the secondary load and the existing mains voltage<br>are matched with each other. The control of the SMPS at pin1 achieved as follows: R102 as a part of control<br>voltage driver (R102, R103 and R104) is variably bypassed by means of the transistor resistance of the op-<br>to-coupler which depends on the respective horizontal voltage.                                                                              |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN2   | Terminal for primary current rise simulation, where an RC network is connected. The voltage rise at pin 2 (sawtooth voltage caused by the charging of C106 through R106 and fast discharging through pin 2) simulates the current rise in the primary winding of the SMPS transformer when the transistor is conducting. When the voltage level reaches the level that is derived from the control voltage at pin 1, the output terminal is set to the ground level terminating the conductivity of Q101. The correct definition of the RC network elements will result a maximum power at the overload. |

| PIN3 : | Primary voltage detector I101, compares the output voltage at pin3 of the TDA4605-3 which is divided by R106 and R107, with an internal reference voltage and disables the SMPS in case of under voltage (mains approx. 150VAc). If this voltage is greater than the threshold value compensation controlled by pin 2 occurs.                                                                                                                                                                                                                                                                            |

| PIN4   | :GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIN5   | Switching pulse output, provide control pulses for switching of Q101. This pin provides an output of +/-1A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PIN6   | Supply voltage pin. A stable internal reference voltage as well as the switching threshold for the supply volta-<br>ge detector are derived from the supply voltage. When the system is switched on the current that is needed<br>is supported through R125 by the transformer winding 7-9.                                                                                                                                                                                                                                                                                                              |

| PIN7   | Soft start terminal where C104 is connected. The short pulses because of this capacitor will cause the star-<br>ting-up to be softly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PIN8   | Zero crossing detector-in the transient state voltage causes a positive output pulse to emerge at pin 5 at every zero transition of the feedback voltage (falling edge).                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### **C-Starting Voltage**

After switching on the receiver with the mains button, approximately 320V is present on the charging capacitor C109. Through the resistor R125 the supply voltage of I101 (pin 6) rises to 12 V. Also 5 Vstby supply from the standby power the supply stage is present.

#### **D-Power Supply**

The power supply for the receiver employs a freerunning switched mode power supply stage with a switching frequency of 35KHz at maximum and I90KHz at minimum load and with a maximum power of 200W. For this reason, a Power Field Effect Transistor is required for the high voltage transistor Q101. The I101 is responsible for driving the MOS power transistor Q101 and also for all control and monitoring functions in the power supply. At Standby mode, the switched mode power supply circuit is switched off. The power consumption is approximately 2W. In this mode, only the  $\mu$ p stage and tuning module is fed with +5Vstby from the "standby" power transformer.

#### **E-Operation**

At pin 2 of I101, a saw tooth signal is present and this has a lower reversal point at approx. 1,1V and an upper reversal point at 2,2V. This saw tooth signal is compared by a comparator with the input current at pin1. If the saw tooth signal exceeds the level at pin1, the comparator switches off the high voltage transistor Q101. In order to switch on the transistor again, there must be a zero-cross over signal at pin8. This pin is connected to the transformer winding 2/4 to identify the zero cross-over.

#### **F-The Control**

If the transformer is overloaded, all voltages reduce. For controlling the voltage drop, diode D101 is used. Like the voltages when the transformer is loaded, also the voltage on diode D101 decreases resulting a decreased input current of I101-(pin 1). In this case the conduction time of the transistor Q101 increases.

As the operating supply for the line output stage effects the line width, it is necessary for the +B voltage (operating supply for the line output stage) to be stable.

Rising in +B causes the voltage of the optocoupler 1102 to decrease. The LED in the optocoupler becomes brighter and the internal transistor between pins 4 and 5 becomes less resistive. This causes the voltage of 1101-(pin1) to increase and the conducting time of the high voltage transistor compared with the sawtooth on pin 2 shorter. As a result the +B supply reduces.

#### **G-Overcurrent Protection**

The lcs (1101) internal circuit monitors the driving pulses of the switching transistor Q101 by means of the voltage the sawtooth signal at pin 2 of 1101. The saw tooth voltage on 1101 -(pin2), supplies the monitoring of the driving pulses to the switching transistor Q101. If too much current flows through the Power-MOS transistor during an over-load of the power supply, the 1101 automatically switches the power supply off.

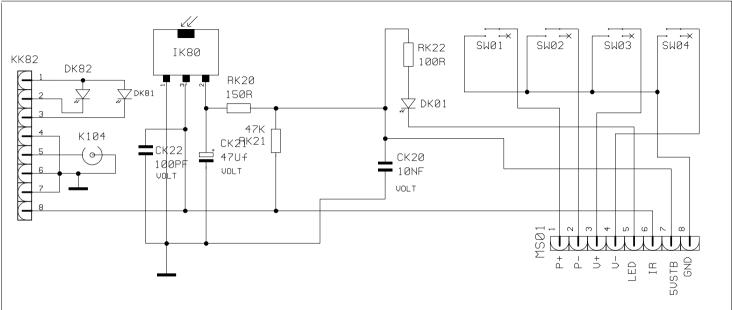

# 2- CONTROL UNIT:

### **A-General Description**

The infra-red receiver decodes the infra-red bi-phase signals for  $\mu$ P I701, the master processor. Also the IR-processor can switch the power supply on or off.

The master processor is responsible for the control of the whole system of TV receiver. The set-up data and the settings are stored in the EEPROM 1703 and the system control programme is stored in the EPROM 1702.

The control and command functions are carried out by the 8bit microcontroller SDA5250 co-operating with the EEPROM I703 and EPROM I702.

Since the microcontroller itself does not include a ROM space, the required operating system will be obtained by using an external EPROM 1702. External EP-ROM contains the specific software program which corresponds to the system of the TV set. The power supply of the microcontroller is realised by the standby power supply unit (50mA). The low active reset pin 28 is kept as low level for at least 10ms by means of trigger circuit Q701 and Q702 when the mains voltage is applied by switching on the TV set. 18 MHz quartz device X701 acts as a clock generator. Q708, Q709, Q710 and Q711 act as a buffer for supporting all of the IIC BUS ICs. Q704, Q705, Q706 and Q707 are buffer transistors for OSD.

### B- Service and Special Functions Using RC (Remote control)

A) When the EPROM I702 is out of work and should be changed, the service technician should order a new EPROM according to the version number which is written on the IC. EPROM includes the system software (BIOS) for TV. B) When the EEPROM 1703 is out of work and should be changed, the service technician should follow the below steps in order to supply the necessary adjustments. Menu including the deflection and colour data can be loaded via remote controller.

"M" button at RC

Move the cursor to " Service" linc with P+/- button

Press "OK" button

\*\*\* Enter code number to the line "for authorized dealer------"

as "089"

The service menu will appear as follows:

Factory Set Values Geometry Video Tuner Parameters

#### Factory Set Values:

This function provides the user fast programming without using the menus. This function is especially for the production line at the factory.

Move the cursor to this line

#### $\mathsf{Press} \downarrow \mathsf{OK}$

TV will automatically switch to the \*\*\* line. If the TV is switched off and switch on again it will automatically switch from the Automatic Search Mode. During the production process at the factory setting this function is the last step before the packing of the set, so the user can have the Automatic Program Search very quickly for the very first time.

(See the related section at the User Manual)

#### Geometry :

This function provides the service technician to adjust the geometry parameters very quickly in any repair process. These parameters and their step ranges are as follows.

| H-Shift      | : steps:0-63 |

|--------------|--------------|

| H-Amplitude  | : steps:0-63 |

| S-Correction | : steps:0-63 |

| V-Amplitude  | : steps:0-63 |

| V-Shift       | : steps:0-7  |

|---------------|--------------|

| E/W Amplitude | : steps:0-63 |

| E/W- Shape    | : steps:0-63 |

| E/W- Tilt     | : steps:0-7  |

You should store these set values by moving the cursor to the "memorize" line.

#### Video:

This function provides the operator at the factory or the service technician to adjust the White Balance parameters.

| Red Gain    | : Red adjustment at max.<br>Beam current                              |

|-------------|-----------------------------------------------------------------------|

| Green Gain  | : Green adjustment at max.<br>Beam current                            |

| Blue Gain   | : Blue adjustment at max.<br>Beam current                             |

| Red Level   | : Red adjustment at<br>min. Beam current                              |

| Green Level | : Green adjustment at min.<br>Beam current                            |

| Blue Level  | : Blue adjustment at min.<br>Beam current                             |

| Peak White  | : It is for the screen adjust ment                                    |

| Grid 2 Adj  | : This adjustment is used at<br>the factory during the<br>production. |

You should store these set values by moving the cursor to the "memorize" line.

**Tuner Parameters :** These values are fixed values and should not be changed.

EHT Compensation: 17

AGC Adjust

: This value should be kept as it is, unless the EEPROM is changed. Otherwise it should be adjusted until not having a snowy picture.

# C) Feature Box

Feature Box is completely shielded as it is the most important and sensitive part of 100 Hz Chassis. The YUV signals which are for 50Hz are converted to 100Hz signals by means of sampling and scanning twice of each sampled signal. Inside of the feature box there are Analog-to-Digital converter, Clock Synchronisation Generator, Memory Synchronisation Generator, Digital-to-Analog Converter and Sequential Access Memory. The input signals to the Feature Box are Horizontal Sync, Vertical Sync, CVBS and YUV signals, SDA, SCL and LLC as well as 5V supply and ground. Analog YUV signals are converted to the digital signals at ADC by means of the synchronisation pulses from SDA9257 which uses analog CVBS signal for providing the necessary sync pulses. The ADC conversion are processed at SDA9205. SDA9220 is responsible for driving the SDA9254 (TV- Sequential Access Memory) and generating sync signals. Together with the other devices of the Feature Box it enhances picture quality. SDA9254 is a combination of the TV sequential access memory and an adaptive filter which is used to enhance noisy input signals. SDA9280 is a Display Processor which accepts four different data input formats. These are IIC, Y, B-Y, R-Y. The input data are digital but the output are analog. This IC is the last step at the feature box .

## **3- DEFLECTION UNIT**

The programmable deflection processor TDA9151B provides the driving pulses required for driving the horizontal and vertical output stages operating according to the 100Hz deflection principle. Apart from these, the above mentioned processor is also used for controlling the east-west circuit, carrying out a switch-off function (protection circuit) and providing the super sand castle pulse (SSC100) for the video signal amplifier. This processor is controlled via an I<sup>2</sup>C BUS and receives the synchronisation pulses from the IPQ-BOX (as well as LLC-signal (line locked signal)).

#### PIN 1: Horizontal Flyback Input

Input pin for retrace pulses having an amplitude of 100Vpp by means of capacitive divider C208/C209. The retrace pulse is needed for the phase control of the driving pulse and the SSC pulse.

#### PIN 2: Display Super Sand Castle Input /Output

From this terminal a double-level SC pulse is provided. The first level i.e. 2.5V is for horizontal and vertical blanking where as the second level i.e. 4,5V is used for video clamping. Further more at pin2 the vertical deflection process is monitored. That means, in case of missing vertical pulses from I202( pin8), pin2 will be locked to 2,5V and the video channel will be controlled to black level.

#### PIN 6: EAST-WEST GEOMETRY OUTPUT

Output for east-west geometry provides the adjustment of horizontal deflection amplitude, picture width, parabolic east-west correction, east-west pin cushion correction and also parabolic correction of trapezium distortions.

#### **PIN 7: EHT COMPENSATION**

EHT compensation pin is an input for keeping the picture size constant although the value of EHT voltage changes (delivered from aquadac coating of the picture tube).

\*\*\*The EHT voltage transformer provides following voltages:

EHT voltage 30KVDc.

Focusing and G2 voltage.

Filament voltage for picture tube.

- +17Vdc

- +40Vdc

- +220Vdc.

In order to be able to adjust the horizontal amplitude of the picture (picture width) and the raster correction independently from the EHT voltage, the line output stage is connected to a diode modulator. One branch of the bridge consists of C211 and C212, another one consists of deflection coil, linearity coil, C213, and the bridge coil L207. At the diagonal branch C215 is placed where as part of the trace capacitance it simultaneously contributes to the internal pincushion correction. The control circuit of the EAST-WEST correction is connected via L204.

#### PIN 8:

Pin8 is designed to determine the reference current for the complete vertical deflection current.

#### PIN 9:

Pin 9 is for flash over protection and is not used at this chassis,

#### PIN 10:

This pin represents the output terminal for the vertical synchronisation. Pulse is the drive input of the differential amplifier stage belonging to the vertical output.

#### PIN 11:

At this IC via  $l^2$ CBUS, it is possible to adjust the following values:

Amplitude of vertical deflection signal 80%, tangential correction from 0 to 16%, vertical shift centering in 7 steps from - 1,5% to +1,5% and 16/9 change-over.

#### Pin 12: VA Input

The vertical synchronisation input coming from the Feature Box

#### PIN 13: HA Input

Horizontal synchronisation input coming from the Feature Box.

#### PIN 14: LLC Input

This signal is for the line and vertical oscillator. Without LLC signal (27MHz) this IC can not operate.

# COMPONENT DESCRIPTIONS

1) TDA4780 2) TDA4665 3) TDA9143 4) SAA4961 5) TDA4470 6) TDA9151 7) TDA8540 8) TDA8351 9) TDA9875-A 10) TDA2616 11) TDA4605-3 12) TDA6111Q 13) M27C2001 14) ST24C16 15) SAA7710 16) TDA7053 A 17) SDA5250

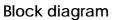

# TDA4780 RGB Video Processor with Automatic Cut-off control and Gamma Adjust

# **GENERAL DESCRIPTION**

The TDA4780 is a monolithic integrated circuit with a luminance and a colour difference interface for video processing in TV receivers. Its primary function is to process the luminance and colour difference signals from a colour decoder which is equipped e.g. with the multistandard decoder TDA4655 or TDA9160 plus delayline TDA4661 or TDA4665 and the Picture Signal Improvement (PSI) IC TDA467X or from a feature module.

The required input signals are:

Luminance and negative colour difference signals Two sets of analog RGB colour signals can also inserted, e.g. one from a peritelevision connector (SCART plug) and the other one from an On-Screen Display (OSD) generator. The TDA4780 has I<sup>2</sup>C-bus control of all parameters and functions with automatic cut-off control of the picture tube cathode currents.

It provides RGB output signals for the video output stages. In clamped output mode it can also be used as an RGB source.

- ◆ 2 or 3-level sandcastle pulse for internal timing pulse generation

- ♦ I<sup>2</sup>C-bus data and clock signals.

### FEATURES

- ♦ Gamma adjust

- Dynamic black control (adaptive black)

- ◆ All input signals clamped on black-levels

- Automatic cut-off control, alternative: output clamping on fixed levels

- Three adjustable reference voltage levels via l<sup>2</sup>Cbus for automatic cut-off control

- ◆ Luminance/colour difference interface

- Two luminance input levels allowed

- Two RGB interfaces controlled by either fast switches or by I<sup>2</sup>C-bus

- Two peak drive limiters, selection via I<sup>2</sup>C-bus

- ◆ Blue stretch, selection via I<sup>2</sup>C-bus

- Luminance output for scan velocity modulation (SCAVEM)

- Extra luminance output; same pin can be used as hue control output e.g. for the TDA4650 and TDA4655

- Non standard operations like 50 Hz/32 kHz are also

- possible

- Either 2 or 3 level sandcastle pulse applicable

- $\blacklozenge$  High bandwidth for 32 kHz application

- ♦ White point adjusts via l<sup>2</sup>C-bus

- Average beam current and improved peak drive limiting

- Two switch-on delays to prevent discoloration during start-up

- All functions and features programmable via I<sup>2</sup>Cbus

- ◆ PAL/SECAM or NTSC matrix selection.

| FSW <sub>2</sub>  | U                              |

|-------------------|--------------------------------|

| R <sub>2</sub> 2  | 27 SDA                         |

| G <sub>2</sub> 3  | 26 YHUE                        |

| B <sub>2</sub> 4  | 25 C <sub>R</sub>              |

| V <sub>P</sub> 5  | 24 R <sub>0</sub>              |

| -(B - Y) 6        | 23 C <sub>G</sub>              |

| -(R - Y) 7        | 22 G <sub>0</sub>              |

| Y 8               | 21 G <sub>B</sub>              |

| GND 9             | 20 B <sub>O</sub>              |

| R <sub>1</sub> 10 | 19 CI                          |

| G1 11             | 18 C <sub>PDST</sub>           |

| B1 12             | 17 CL                          |

| FSW1 13           | <sup>16</sup> C <sub>PDL</sub> |

| SC 14             | 15 BCL                         |

| Pin Connections   |                                |

#### PINNING

| SYMBOL            | PIN | DESCRIPTION                                               |

|-------------------|-----|-----------------------------------------------------------|

| FSW <sub>2</sub>  | 1   | fast switch 2 input                                       |

| R <sub>2</sub>    | 2   | red input 2                                               |

| G <sub>2</sub>    | 3   | green input 2                                             |

| B <sub>2</sub>    | 4   | blue input 2                                              |

| V <sub>p</sub>    | 5   | supply voltage                                            |

| -(B - Y)          | 6   | colour difference input –(B - Y)                          |

| –(R - Y)          | 7   | colour difference input –(R - Y)                          |

| Υ                 | 8   | luminance input                                           |

| GND               | 9   | ground                                                    |

| R <sub>1</sub>    | 10  | red input 1                                               |

| G <sub>1</sub>    | 11  | green input 1                                             |

| B <sub>1</sub>    | 12  | blue input 1                                              |

| FSW <sub>1</sub>  | 13  | fast switch 1 input                                       |

| SC                | 14  | sandcastle pulse input                                    |

| BCL               | 15  | average beam current limiting input                       |

| C <sub>PDL</sub>  | 16  | storage capacitor for peak limiting                       |

| CL                | 17  | storage capacitor for leakage current compensation        |

| C <sub>PDST</sub> | 18  | storage capacitor for peak dark                           |

| CI                | 19  | cut-off measurement input                                 |

| B <sub>0</sub>    | 20  | blue output                                               |

| CB                | 21  | blue cut-off storage capacitor                            |

| G <sub>0</sub>    | 22  | green output                                              |

| C <sub>G</sub>    | 23  | green cut-off storage capacitor                           |

| R <sub>0</sub>    | 24  | red output                                                |

| C <sub>R</sub>    | 25  | red cut-off storage capacitor                             |

| YHUE              | 26  | Y-output/hue adjust output                                |

| SDA               | 27  | I <sup>2</sup> C-bus serial data input/acknowledge output |

| SCL               | 28  | I <sup>2</sup> C-bus serial clock input                   |

### QUICK REFERENCE DATA

| SYMBOL              | PARAMETER                                                          | Min. | Тур.      | Max. | Unit |

|---------------------|--------------------------------------------------------------------|------|-----------|------|------|

| V <sub>P</sub>      | supply voltage (pin5)                                              | 7.2  | 8.0       | 8.8  | V    |

| I <sub>P</sub>      | supply current (pin5)                                              | 8.0  | 100       | 120  | mA   |

| V <sub>8(p-p)</sub> | luminance input (peak-to-peak value) (C)VBS                        | -    | 0.45/1.43 | -    | V    |

| V <sub>6(p-p)</sub> | –(B - Y) input (peak-to-peak value)                                | -    | 1.33      | -    | V    |

| V <sub>7(p-p)</sub> | –(R - Y) input (peak-to-peak value)                                | -    | 1.05      | -    | V    |

| V <sub>14</sub>     | three-level sandcastle pulse                                       |      |           |      |      |

|                     | H+V                                                                | -    | 2.5       | -    | V    |

|                     | Н                                                                  | -    | 4.5       | -    | V    |

|                     | ВК                                                                 |      | 8.0       | -    | V    |

|                     | two-level sandcastle pulse                                         |      |           |      |      |

|                     | H+V                                                                | -    | 2.5       | -    | V    |

|                     | ВК                                                                 | -    | 4.5       | -    | V    |

| V <sub>i</sub>      | RGB input signals at pins 2,3,4,10,11 and 12(black-to-white value) |      | 0.7       | -    | V    |

| V <sub>o(p-p)</sub> | RGB output at pins 24, 22 and 20(black-to-white value)             |      | 2.0       | -    | V    |

| T <sub>amb</sub>    | operating ambient temperature                                      | -20  | -         | +70  | °C   |

### FUNCTIONAL DESCRIPTION

#### Signal input stages

The TDA4780 contains 3 sets of input signal stages for:

1.Luminance/colour-difference signals: a) Y: 0.45 V (p-p) VBS or 1.43 V (p-p) VBS, selectable via I2C-bus.

b) -(R - Y): 1.05 V (p-p).

c) -(B - Y): 1.33 V (p-p).

The capacitively coupled signals are matrixed to RGB signals by either a PAL/SECAM or NTSC matrix (selected via l<sup>2</sup>C-bus).

- 2.(RGB)<sub>1</sub> signals (0.7 V (p-p) VB), capaci tively coupled (e.g. from external sour ce).

- 3.(RGB)<sub>2</sub> signals (0.7 V (p-p) VB), capaci tively coupled (e.g. videotext, OSD).

All input signals are clamped in order to have the same black levels at the signal switch input. Displayed signals must be synchronous with the sandcastle pulse.

#### Signal switches

Both fast signal switches can be operated by switching pins (e.g. SCART facilities) or set via the  $l^2$ C-bus. With the pin FSW<sub>1</sub> the Y-CD signals or the (RGB)<sub>1</sub> signals can be selected, with pin FSW<sub>2</sub> the above selected signals or the (RGB)<sub>2</sub> signals are enabled. During the vertical and horizontal blanking time an artificial black level equal to the clamped black level is inserted in order to clip off the sync pulse of the luminance signal and to suppress hum during the cut-off measurement time and eliminate noise during these intervals.

#### Saturation, contrast and brightness adjust

Saturation, contrast and brightness adjusts are controlled via the I<sup>2</sup>C-bus and act on Y, CD as well as on RGB input signals. Gamma acts on the luminance content of the input signals.

#### Gamma adjust

The gamma adjust stage has a non-linear transmission characteristic according to the formula  $y = x^{gamma}$ , where x represents the input and y the output signal. If gamma is smaller than unity, the lower parts of the signal are amplified with higher gain.

#### Automatic cut-off control

During leakage measurement time the leakage current is compensated in order to get a reference voltage at the cut-off measurement info pin. This compensation value is stored in an external capacitor. During cut-off current measurement times for the R, G and B channels, the voltage at this pin is compared with the reference voltage, which is individually adjustable via I<sup>2</sup>C-bus for each colour channel. The control voltages that are derived in this way are stored in the external feedback capacitors. Shift stages add these voltages to the corresponding output signals. The automatic cut-off control may be disabled via the I<sup>2</sup>C-bus. In this mode the output voltage is clamped to 2.5 V. Clamping periods are the same as the cut-off measurement periods.

#### Adaptive black (ADBL)

The adaptive black stage detects the lowest voltage of the luminance component of the internal RGB signals during the scanning time and shifts it to the nominal black level. In order to keep the nominal white level the contrast is increased simultaneously.

#### Blue stretch (BLST)

The blue stretch channel gets additional amplification if the blue signal is greater than 80% of the nominal signal amplitude. In the event the white point is shifted towards higher colour temperature so that white parts of a picture seem to be brighter.

#### Measurement pulse and blanking stage

During the vertical and horizontal blanking time and the measurement period the signals are blanked to an ultra black level, so the leakage current of the picture tube can be measured and automatically compensated for.

During the cut-off measurement lines (one line period for each R, G or B) the output signal levels are at cut-off measurement level.

The vertical blanking period is timed by the sandcastle pulse. The measurement pulses (le-akage, R, G and B) are triggered by the negative going edge of the vertical pulse of the sandcastle pulse and start after the following horizontal pulse.

The IC is prepared for  $2f_H$  (32 kHz) application.

# Output amplifier and white adjust potentiometer

The RGB signals are amplified to nominal 2 V (p-p), the DC-levels are shifted according to cut-off control.

The nominal signal amplitude can be varied by  $\pm 50\%$  by the white point adjustment via the l<sup>2</sup>C-bus (individually for RGB respect).

#### Signal limiting

The TDA4780 provides two kinds of signal limiting.

First, an average beam limiting, that reduces signal level if a certain average is exceeded. Second, a peak drive limiting, that is activated if one of the RGB signals even shortly exceeds a via I<sup>2</sup>C-bus adjusted threshold. The latter can be either referred to the cut-off measurement level of the outputs or to ground.

When signal limiting occurs, contrast is reduced, and at minimum contrast brightness is reduced additionally.

#### Sandcastle decoder and timer

A 3-level detector separates the sandcastle pulse into combined line and field pulses, line pulses, and clamping pulses. The timer contains a line counter and controls the cut-off control measurement.

Application with a 2-level 5 V sandcastle pulse is possible.

#### Switch on delay circuit

After switch on all signals are blanked and a warm up test pulse is fed to the outputs during the cut-off measurement lines. If the voltage at the cut-off measurement input exceeds an internal level the cut-off control is enabled but the signal remains still blanked. In the event of output clamping, the cut-off control is disabled and the switch on procedure will be skipped.

#### Y output and hue adjust

The TDA4780 contains a D/A converter for hue adjust. The analog information can be fed, e.g. to the multistandard decoder TDA4650 or TDA4655. This output pin may be switched to a Y output signal, which can be used for scan velocity modulation (SCAVEM). The Y output is the Y input signal or the matrixed (RGB) input signal according to the switch position of the fast switch.

#### l<sup>2</sup>C-bus

The TDA4780 contains an I<sup>2</sup>C-bus receiver for control function.

#### **ESD** protection

The Pins are provided with protection diodes against ground and supply voltage (see Chapter "internal pin configurations"). I<sup>2</sup>C-bus input pins do not shunt the I<sup>2</sup>C-bus signals in the event of missing supply voltage.

#### EMC

The pins are protected against electromagnetic radiation.

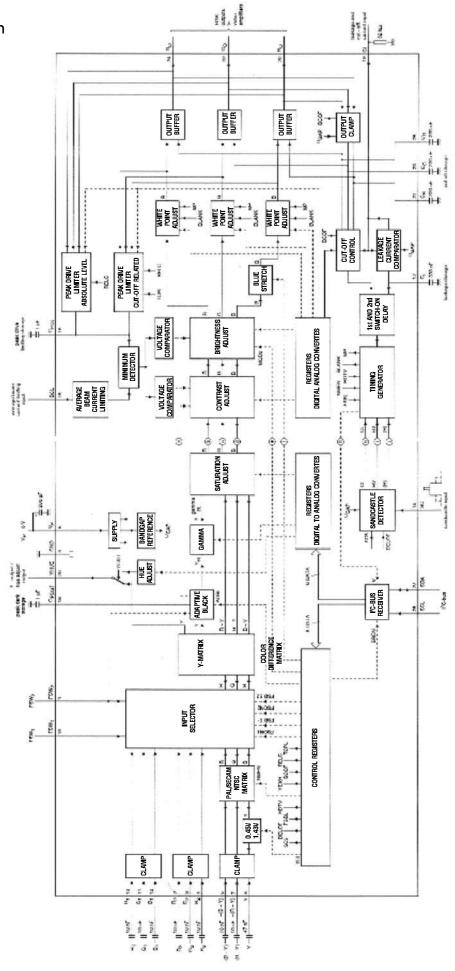

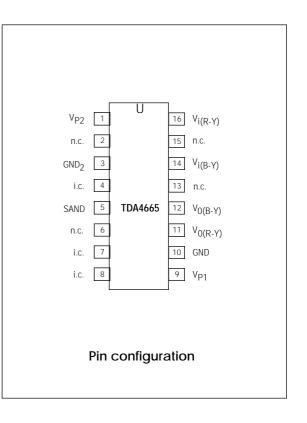

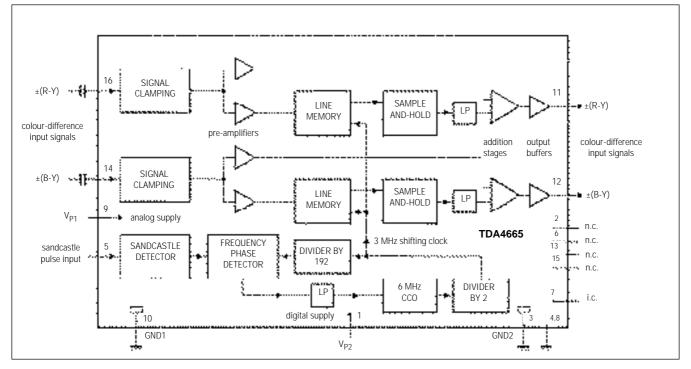

# TDA4665 Baseband Delay Line

#### **GENERAL DESCRIPTION**

The TDA4665 is an integrated baseband delay line circuit with one line delay.. It is suitable for decoders with colour-difference signal outputs  $\pm$ (R-Y) and  $\pm$ (B-Y)

#### FEATURES

- $\blacklozenge$  The comb filters, using the switched-capacitor technique, for one line delay time (64  $\mu s)$

- ◆ Adjustment-free application

- No crosstalk between SECAM colour carriers (diaphoty)

- ◆ Handles negative or positive colour-difference input signals

- $\bullet$  Clamping of AC-coupled input signals  $\pm$ (R-Y) and  $\pm$ (B-Y))

- ◆ VCO without external components

- 3 MHz internal clock signal derived from a 6MHz CCO, line-locked by the sandcastle pulse (64 μs line)

- ◆ Sample and hold circuits and low-pass filters to suppress the 3 MHz clock signal

- ◆ Addition of delayed and non-delayed output signals

- Output buffer amplifiers

- Comb filtering functions for NTSC colour-difference signals to suppress cross-colour)

| SYMBOL              | PIN | DESCRIPTION                         |

|---------------------|-----|-------------------------------------|

| V <sub>P2</sub>     | 1   | +5V supply voltage for digital part |

| n.c.                | 2   | not connected                       |

| GND2                | 3   | ground for digital part (0V)        |

| i.c.                | 4   | internally connected                |

| SAND                | 5   | sandcastle pulse input              |

| n.c.                | 6   | not connected                       |

| i.c.                | 7   | internally connected                |

| i.c.                | 8   | internally connected                |

| V <sub>P1</sub>     | 9   | +5V supply voltage for analog part  |

| GND1                | 10  | ground for analog part (0V)         |

| V <sub>0(R-Y)</sub> | 11  | ±(R–Y) output signal                |

| V <sub>0(B-Y)</sub> | 12  | ±(B–Y) output signal                |

| n.c.                | 13  | not connected                       |

| V <sub>i(B-Y)</sub> | 14  | ±(B-Y) input signal                 |

| n.c.                | 15  | not connected                       |

| V <sub>i(R-Y)</sub> | 16  | ±(R–Y) input signal                 |

#### PINNING

#### QUICK REFERENCE DATA

| SYMBOL              | PARAMETER                                                               | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------------------------------------------------------|------|------|------|------|

| V <sub>P1</sub>     | analog supply voltage (pin9)                                            | 4.5  | 5    | 6    | V    |

| V <sub>P2</sub>     | digital supply voltage (pin1)                                           | 4.5  | 5    | 6    | V    |

| I <sub>P(tot)</sub> | total supply current                                                    | -    | 5.5  | 7.0  | mA   |

| V <sub>i(p-p)</sub> | ±(R - Y) input signal PAL/NTSC(peak-to-peak value; pin 16)              | -    | 525  | -    | mV   |

|                     | ±(B - Y) input signal PAL/NTSC(peak-to-peak value; pin 14)              | -    | 665  | -    | mV   |

|                     | ±(R - Y) input signal SECAM (peak-to-peak value; pin 16)                | -    | 1.05 | -    | V    |

|                     | ±(B - Y) input signal SECAM (peak-to-peak value; pin 14)                | -    | 1.33 | -    | V    |

| G <sub>V</sub>      | gain V <sub>O</sub> /V <sub>i</sub> of colour-difference output signals |      |      |      |      |

|                     | $V_{11}$ / $V_{16}$ for PAL and NTSC                                    | 5.3  | 5.8  | 6.3  | dB   |

|                     | $V_{12}$ / $V_{14}$ for PAL and NTSC                                    |      | 5.8  | 6.3  | dB   |

|                     | V <sub>11</sub> / V <sub>16</sub> for SECAM                             |      | -0.1 | +0.4 | dB   |

|                     | V <sub>12</sub> / V <sub>14</sub> for SECAM                             | -0.6 | -0.1 | +0.4 | dB   |

#### Block diagram

#### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134). Ground pins 3 and 10 connected together.

| SYMBOL           | PARAMETER                            | Min. | Max.                 | Unit |

|------------------|--------------------------------------|------|----------------------|------|

| V <sub>P1</sub>  | analog supply voltage (pin9)         | -0.5 | +7                   | V    |

| V <sub>P2</sub>  | digital supply voltage (pin1)        | -0.5 | +7                   | V    |

| V <sub>5</sub>   | voltage on pin 5                     | -0.5 | V <sub>P</sub> + 1.0 | V    |

| V <sub>n</sub>   | voltage on pins 11, 12, 14 and 16    | -0.5 | VP                   | V    |

| т <sub>stg</sub> | storage temperature                  | -25  | +150                 | °C   |

| T <sub>amb</sub> | operating ambient temperature        | 0    | 70                   | °C   |

| V <sub>ESD</sub> | electrostatic handling for all pins; | -    | ±500                 | V    |

### CHARACTERISTICS

| SYMBOL                                     | PARAMETER                                                                    | CONDITIONS                           | Min.                 | Тур.   | Max.                 | Unit |  |

|--------------------------------------------|------------------------------------------------------------------------------|--------------------------------------|----------------------|--------|----------------------|------|--|

| Supply                                     |                                                                              |                                      |                      |        |                      |      |  |

| V <sub>P1</sub>                            | analog supply voltage (pin9)                                                 |                                      | 4.5                  | 5      | 6                    | V    |  |

| V <sub>P2</sub>                            | digital supply voltage (pin1)                                                |                                      | 4.5                  | 5      | 6                    | V    |  |

| I <sub>P1</sub>                            | analog supply current                                                        |                                      | -                    | 4.8    | 6.0                  | mA   |  |

| I <sub>P2</sub>                            | digital supply current                                                       |                                      | _                    | 0.7    | 1.0                  | mA   |  |

|                                            | ence input signals                                                           |                                      |                      | 0.7    | 1.0                  |      |  |

| V <sub>i(p-p)</sub>                        | input signal (peak-to-peak value)                                            |                                      |                      |        | 1                    |      |  |

| • I(p-p)                                   | $\pm$ (R - Y) PAL and NTSC (pin 16)                                          |                                      | -                    | 525    | -                    | mV   |  |

|                                            | $\pm$ (B - Y) PAL and NTSC (pin 14)                                          |                                      | _                    | 665    | -                    | mV   |  |

|                                            | $\pm$ (R - Y) SECAM (pin 16)                                                 |                                      | _                    | 1.05   | _                    | V    |  |

|                                            | $\pm$ (R - Y) SECAM (pin 16)<br>$\pm$ (B - Y) SECAM (pin 14)                 |                                      | _                    | 1.33   | _                    | V    |  |

| V., y, y                                   | maximum symmetrical input signal                                             |                                      |                      | 1.55   |                      | v    |  |

| V <sub>i(max)(p-p)</sub>                   | (peak-to-peak value)                                                         |                                      |                      |        |                      |      |  |

|                                            | $\pm$ (R - Y) or $\pm$ (B - Y) for PAL and NTSC                              | before clipping                      | 1                    | _      | _                    | V    |  |

|                                            | $\pm$ (R - Y) or $\pm$ (B - Y) for SECAM                                     | before clipping                      | 2                    |        | _                    | V    |  |

| R <sub>14, 16</sub>                        | input resistance during clamping                                             | berore enppring                      | 2                    | _      | 40                   | k    |  |

| C <sub>14, 16</sub>                        | input capacitance                                                            |                                      |                      |        | 10                   | pF   |  |

| V <sub>14, 16</sub><br>V <sub>14, 16</sub> | input clamping voltage                                                       | proportional to Vp                   | 1.3                  | 1.5    | 1.7                  | V    |  |

|                                            |                                                                              |                                      | 1.5                  | 1.5    | 1.7                  | v    |  |

|                                            | ence output signals                                                          |                                      |                      |        |                      |      |  |

| V <sub>o(p-p)</sub>                        | output signal (peak-to-peak value)                                           | all atomdarda                        |                      | 1.05   |                      | V    |  |

|                                            | ±(R - Y) on pin 11                                                           | all standards                        | -                    | 1.05   | -                    | -    |  |

|                                            | ±(B - Y) on pin 12                                                           | all standards                        | -                    | 1.33   | -                    | V    |  |

| V <sub>11</sub> , V <sub>12</sub>          | ratio of output amplitudes at equal input signals                            | V <sub>i(14,16)(p-p)</sub> = 1.33 V  | -0.4                 | 0      | +0.4                 | dB   |  |

| V <sub>11, 12</sub>                        | DC output voltage                                                            | proportional to Vp                   | 2.5                  | 2.9    | 3.3                  | V    |  |

| R <sub>11, 12</sub>                        | output resistance                                                            |                                      | -                    | 330    | 400                  | 10   |  |

| Gv                                         | gain for PAL and NTSC                                                        | ratio V <sub>0</sub> /V <sub>i</sub> | 5.3                  | 5.8    | 6.3                  | dB   |  |

|                                            | gain for SECAM                                                               | ratio V <sub>0</sub> /V <sub>i</sub> | -0.6                 | -0.1   | +0.4                 | dB   |  |

| V <sub>0/</sub> V <sub>0+1</sub>           | ratio of delayed to non-delayed output                                       | $V_{i(14,16)(p-p)} = 1.33 V;$        | -0.1                 | 0      | +0.1                 | dB   |  |

|                                            | signals (pins 11 and 12)                                                     | SECAM signals                        |                      |        |                      |      |  |

| V <sub>n(rms)</sub>                        | noise voltage (RMS value pins 11 and 12)<br>unwanted signals (line - locked) | V <sub>i(14,16)</sub> = 0 V; note 2  | -                    | -      | 1.2                  | mV   |  |

| V <sub>(11, 12)</sub> (p-p)                |                                                                              | V <sub>i(14,16)</sub> = 0 V; active  |                      |        |                      |      |  |

|                                            | (peak-to-peak value)                                                         | video; Rs = 300                      |                      |        |                      |      |  |

|                                            | meander                                                                      |                                      | -                    | -      | 5                    | mV   |  |

|                                            | spikes                                                                       |                                      | -                    | -      | 10                   | mV   |  |

| S/N(W)                                     | weighed signal-to-noise ratio (pins 11 and 12)                               | $V_{0(p-p)} = 1 V$                   | -                    | 54     | -                    | dB   |  |

| t <sub>d</sub>                             | time difference between non-delayed and                                      |                                      | 63.94                | 64     | 64.06                | μs   |  |

|                                            | delayed output signals (pins 11 and 12)                                      |                                      |                      |        |                      |      |  |

| t <sub>d</sub>                             | delay of non-delayed signals                                                 |                                      | 40                   | 60     | 80                   | ns   |  |

| t <sub>tr</sub>                            | transient time of delayed signal on pins 11                                  | 300 ns transient of                  | -                    | 350    | -                    | ns   |  |

|                                            | respectively 12                                                              | SECAM signal                         |                      |        |                      |      |  |

|                                            | transient time of non-delayed signal on pins 11                              | 300 ns transient of                  | -                    | 320    | -                    | ns   |  |

|                                            | respectively 12                                                              | SECAM signal                         |                      |        |                      |      |  |

| Colour-diff                                |                                                                              |                                      |                      |        |                      |      |  |

| f <sub>BK</sub>                            | burst-key frequency/sandcastle frequency                                     |                                      | 14.2                 | 15.625 | 17.0                 | kHz  |  |

| V <sub>t5</sub>                            | top pulse voltage                                                            |                                      | 4.0                  | -      | V <sub>p</sub> + 1.0 | V    |  |

| V <sub>slice</sub>                         | internal slicing level                                                       |                                      | V <sub>5</sub> - 1.0 | -      | V <sub>5</sub> - 0.5 | V    |  |

| I <sub>5</sub>                             | input current                                                                |                                      | -                    | -      | 10                   | μA   |  |

| C <sub>5</sub>                             | input capacitance                                                            |                                      | -                    | -      | 10                   | pF   |  |

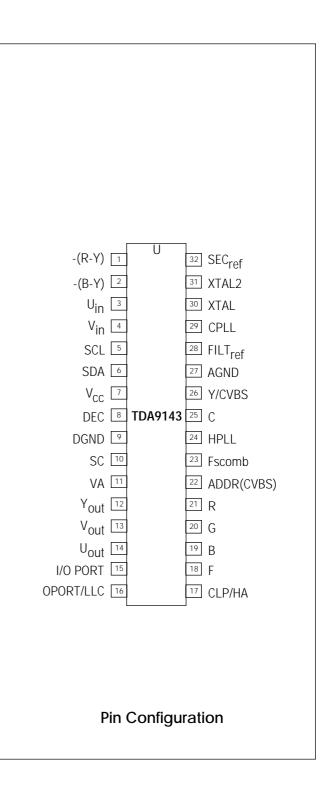

# TDA9143 I<sup>2</sup>C-BUS controlled, alignment-free PAL/NTSC/SECAM Decoder / Sync Processor

#### **GENERAL DESCRIPTION**

The TDA9143 is an 1<sup>2</sup>C-bus controlled, alignment-free PAL/NTSC/SECAM decoder/sync processor with blanking facilities for PALplus and EDTV-2 signals. The TDA9143 has been designed for use with baseband chrominance delay lines, and has a combined subcarrier frequency/comb filter enable signal for communication with a PAL/NTSC comb filter.

The IC can process both CVBS input signals and Y/C input signals. The input signal is available on an output pin, in the event of a Y/C signal, it is added into a CVBS signal.

The sync processor provides a two-level sandcastle, a horizontal pulse (CLP or HA pulse, bus selectable) and a vertical (VA) pulse. When the HA pulse is selected, a line-locked clock (LLC) signal is available at the output port pin (6.75 MHz or 6.875 MHz).

A fast switch can select either the internal Y signal

#### **FEATURES**

- Multi-standard colour decoder and sync processor for PAL, NTSC and SECAM

- PALplus helper blanking and EDTV-2 blanking

- ♦ I<sup>2</sup>C-bus controlled

- ◆ I<sup>2</sup>C-bus addresses hardware selectable

- ◆ Pin compatible with TDA9141

- Alignment free

- Few external components

- Designed for use with baseband delay lines

- Integrated video filters

- ◆ Adjustable luminance delay

- ◆ Noise detector with I<sup>2</sup>C-bus read-out

- Norm/no norm detector with I2C-bus read-out

- CVBS or Y/C input, with automatic detection possibility

- ◆ CVBS output, provided I<sup>2</sup>C-bus address 8A is used

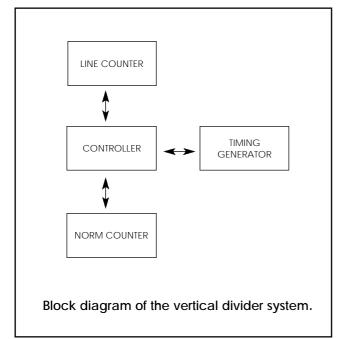

- Vertical divider system

- ◆ Two-level sandcastle signal

- VA synchronization pulse (3-state)

- HA synchronization pulse or clamping pulse CLP input/output

- ◆ Line-locked clock output (6.75 MHz or 6.875 MHz) or stand-alone I<sup>2</sup>C-bus output port

- ◆ Stand-alone I<sup>2</sup>C-bus input/output port

with the UV input signals, or YUV signals made of the RGB input signals. The RGB input signals can be clamped with either the internal or an external clamping signal.

Two pins with an input/output port and an output port of the  $l^2C\mbox{-}bus$  are available.

The I<sup>2</sup>C-bus address of the TDA9143 is hardware programmable.

- ◆ Colour matrix and fast YUV switch

- Comb filter enable input/output with subcarrier frequency

- Internal bypass mode of external delay line for NTSC applications

- Low power standby mode with 3-state YUV outputs

- ◆ Fast blanking detector with I<sup>2</sup>C-bus read-out

- Blanked or unblanked sync on Yout by I<sup>2</sup>C-bus bit BSY

- Internal MACROVISION gating for the horizontal PLL enabled by bus bit EMG.

#### PINNING

| SYMBOL              | PIN | DESCRIPTION                                          |

|---------------------|-----|------------------------------------------------------|

| -(R-Y)              | 1   | output signal for -(R–Y)                             |

| -(B-Y)              | 2   | output signal for -(B-Y)                             |

| U <sub>in</sub>     | 3   | chrominance U input                                  |

| V <sub>in</sub>     | 4   | chrominance V input                                  |

| SCL                 | 5   | serial clock input                                   |

| SDA                 | 6   | serial data input/output                             |

| V <sub>cc</sub>     | 7   | positive supply voltage                              |

| DEC                 | 8   | digital supply decoupling                            |

| DGND                | 9   | digital ground                                       |

| SC                  | 10  | sandcastle output                                    |

| VA                  | 11  | vertical acquisition<br>synchronization pulse        |

| Y <sub>out</sub>    | 12  | luminance output                                     |

| V <sub>out</sub>    | 13  | chrominance V output                                 |

| U <sub>out</sub>    | 14  | chrominance U output                                 |

| I/O PORT            | 15  | input/output port                                    |

| OPORT/LLC           | 16  | output port/line-locked clock output                 |

| CLP/HA              | 17  | clamping pulse/HA synchronization pulse input/output |

| F                   | 18  | fast switch select input                             |

| В                   | 19  | BLUE input                                           |

| G                   | 20  | GREEN input                                          |

| R                   | 21  | RED input                                            |

| ADDR(CVBS)          | 22  | I <sup>2</sup> C-bus address input (CVBS output)     |

| Fscomb              | 23  | comb filter status input/output                      |

| HPLL                | 24  | horizontal PLL filter                                |

| С                   | 25  | chrominance input                                    |

| Y/CVBS              | 26  | luminance/CVBS input                                 |

| AGND                | 27  | analog ground                                        |

| FILT <sub>ref</sub> | 28  | filter reference decoupling                          |

| CPLL                | 29  | colour PLL filter                                    |

| XTAL                | 30  | reference crystal input                              |

| XTAL2               | 31  | second crystal input                                 |

| SEC <sub>ref</sub>  | 32  | SECAM reference decoupling                           |

| SYMBOL                     | PARAMETER                                                   | CONDITIONS           | Min. | Тур. | Max. | Unit |

|----------------------------|-------------------------------------------------------------|----------------------|------|------|------|------|

| V <sub>CC</sub>            | positive supply voltage                                     |                      | 7.2  | 8.0  | 8.8  | V    |

| I <sub>CC</sub>            | supply current                                              |                      | 50   | 60   | 70   | mA   |

| V <sub>CVBS(p-p)</sub>     | CVBS input voltage (peak-to-peak value)                     | top sync-white       | -    | 1.0  | 1.43 | V    |

| V <sub>Y(p-p)</sub>        | luminance input voltage (peak-to-peak value)                | top sync-whit        | -    | 1.0  | 1.43 | V    |

| V <sub>C(p-p)</sub>        | chrominance burst input voltage<br>(peak-to-peak value)     |                      | -    | 0.3  | 0.6  | V    |

| V <sub>Y(out)</sub>        | luminance black-white output voltage                        |                      | -    | 1.0  | -    | V    |

| V <sub>U(out)(p-p)</sub>   | U output voltage (peak-to-peak value)                       | standard colour bar  | -    | 1.33 | -    | V    |

| V <sub>V(out)(p-p)</sub>   | V output voltage (peak-to-peak value)                       | standard colour bar  | -    | 1.05 | -    | V    |

| V <sub>SC(bl)</sub>        | sandcastle blanking voltage level                           |                      | 2.2  | 2.5  | 2.8  | V    |

| V <sub>SC(clamp)</sub>     | sandcastle clamping voltage level                           |                      | 4.2  | 4.5  | 4.8  | V    |

| V <sub>VA(bl)</sub>        | VA output voltage                                           |                      | 4.0  | 5.0  | 5.5  | V    |

| V <sub>HA(bl)</sub>        | HA output voltage                                           |                      | 4.0  | 5.0  | 5.5  | V    |

| V <sub>LLC(p-p)</sub>      | LLC output voltage amplitude<br>(peak-to-peak value)        |                      | 250  | 500  | -    | mV   |

| V <sub>R, G, B</sub> (p-p) | RGB input voltage (peak-to-peak value)                      | 0 to 100% saturation | -    | 0.7  | 1.0  | V    |

| V <sub>clamp(I/O)</sub>    | clamping pulse input(output voltage                         |                      | -    | 5.0  | -    | V    |

| V <sub>sub(p-p)</sub>      | subcarrier output voltage amplitude<br>(peak-to-peak value) |                      | 150  | 200  | 300  | mV   |

| V <sub>OPORT</sub>         | port output voltage                                         |                      | 4.0  | 5.0  | 5.5  | V    |

#### QUICK REFERENCE DATA

### FUNCTIONAL DESCRIPTION

The TDA9143 is an I<sup>2</sup>C-bus controlled, alignment-free PAL/NTSC/SECAM colour decoder/sync processor which has been designed for use with baseband chrominance delay lines. For PALplus and EDTV-2 (60 Hz) signals blanking facilities are included.

In the standard operating mode the  $\mbox{I}^2\mbox{C-bus}$  address is 8A. If the address input is connected to the positive supply rail the address will change to 8E.

#### Input switch

#### CAUTION

The voltage on the chrominance pin must never exceed 5.5 V. If it does, the IC enters a testmode.

The TDA9143 has a two pin input for CVBS or Y/C signals which can be selected via the I<sup>2</sup>C-bus. The input selector also has a position in which it automatically detects whether a CVBS or Y/C signal is on the input. In this input selector position, standard identification first takes place on an added Y/CVBS and C input signal.

After that, both chrominance signal input amplitudes are checked once and the input with the strongest chrominance burst signal is selected. The input switch status is read out by the  $I^2C$ -bus via output bit YC. The auto input detector indicates YC = 1 for a VBS input signal (no chrominance component).

#### CVBS output

In the standard operating mode with I<sup>2</sup>C-bus address 8A, a CVBS output signal is available on the address pin, which represents either the CVBS input signal or the Y/C input signal, added into a CVBS signal.

#### RGB colour matrix

#### CAUTION

The voltage on the Ui, pin must never exceed 5.5 V. If it does, the IC enters a test mode.

The TDA9143 has a colour matrix to convert RGB input signals into YUV signals. A fast switch, controlled by the signal on pin F and enabled by I2C-bus via EFS (enable fast switch), can select between these YUV signals and the YUV signals of the decoder. Mode FRGB = 1 (forced RGB) overrules EFS and switches the matrixed RGB inputs to the YUV outputs.

The Y signal is internally connected to the switch. The -(R-Y) and -(B-Y) output signals of the decoder first have to be delayed in external baseband chrominance delay lines. The outputs of the delay lines must be connected to the UV input pins. If the RGB signals are not synchronous with the selected decoder input signal, clamping of the RGB input signals is possible by I<sup>2</sup>C-bus selection of ECL (external RGB clamp mode) and by feeding an external clamping signal to the CLP pin.

Also in external RGB clamp mode the VA output will

be in a high impedance OFF-state. The YUV outputs can be put in 3-state mode by bus bit LPS (low power standby mode).

#### Standard identification

The standards which the TDA9143 can decode depend upon the choice of external crystals. If a 4.4 MHz and a 3.6 MHz crystal are used then SECAM, PAL 4.4/3.6 and NTSC 4.4/3.6 can be decoded. If two 3.6 MHz crystals are used then only PAL 3.6 and NTSC 3.6 can be decoded.

Which 3.6 MHz standards can be decoded depends upon the exact frequencies of the 3.6 MHz crystals. In an application where not all standards are required only one crystal is sufficient; in this instance the crystal must be connected to the reference crystal input (pin 30). If a 4.4 MHz crystal is used it must always be connected to the reference crystal input. Both crystals are used to provide a reference for the filters and the horizontal PLL, however, only the reference crystal is used to provide a reference for the SECAM demodulator. To enable the calibrating circuits to be adjusted exactly, two bits from I<sup>2</sup>C-bus subaddress 00 are used to indicate which crystals are connected to the IC.

The standard identification circuit is a digital circuit without external components.

The decoder (via the I<sup>2</sup>C-bus) can be forced to decode either SECAM or PAL/NTSC (but not PAL or NTSC). Crystal selection can also be forced. Information concerning standard and which crystal is selected and whether the colour killer is ON or OFF is provided by the read out.

Using the forced-mode does not affect the search loop, it does however prevent the decoder from reaching or staying in an unwanted state. The identification circuit skips impossible standards (e.g. SECAM when no 4.4 MHz crystal is fitted) and illegal standards (e.g. in forced mode). To reduce the risk of wrong identification, PAL has priority over SECAM. Only line identification is used for SECAM. For a vertical frequency of 60 Hz, SECAM can be blocked to prevent wrong identification by means of bus bit SAF.

#### Integrated filters

All chrominance bandpass and notch filters, including the luminance delay line, are an integral part of the IC. The filters are gyrator-capacitor type filters. The resonant frequency of the filters is controlled by a circuit that uses the active crystal to tune the SECAM Cloche filter during the vertical flyback time. The remaining filters and the luminance delay line are matched to this filter. The filters can be switched to either 4.43 MHz, 4.29 MHz or 3.58 MHz. The switching is controlled by the standard identification circuit. The luminance notch used for SECAM has a lower Q-factor than the notch used for PAL/NTSC. The notches are provided with a little preshoot to obtain a symmetrical step response. In Y/C mode the chrominance notch filters are bypassed, to preserve full signal bandwidth. For a CVBS signal the chrominance notch filters can be bypassed by bus selection of bit TB (trap bypass). The delay of the colour difference signals -(R-Y) and -(B-Y) in the chrominance signal path and the external chrominance delay lines when used, can be fitted to the luminance signal by I<sup>2</sup>C-bus in 40 ns steps.

The typical luminance delay can be calculated: delay  $90 + \overline{SAK}$ .  $\overline{SBK}$  {170 + 40( $\overline{FRQTB}$ )} + 160( $\overline{YD3}$ ) + 160( $\overline{YD2}$ ) + 80( $\overline{YD1}$ ) + 40( $\overline{YD0}$ ) [ns].

#### Color decoder

The PAL/NTSC demodulator employs an oscillator that can operate with either crystal (3.6 MHz or 4.4 MHz). If the I<sup>2</sup>C-bus indicates that only one crystal is connected, it will always connect to the crystal on the reference crystal input (pin 30).

The Hue signal which is adjustable by  $I^2C$ -bus, is gated during the burst for NTSC signals.

The SECAM demodulator is an auto-calibrating pLL demodulator which has two references. The reference crystal, to force the PLL to the desired free-running frequency and the bandgap reference, to obtain the correct absolute value of the output signal. The VCO of the PLL is calibrated during each vertical blanking period, when the IC is in search mode or in SECAM mode.

If the reference crystal is not 4.4 MHz the decoder will not produce the correct SECAM signals. Especially for NTSC applications an internal bypass mode of the external baseband delay line (for instance TDA4665) is added, controlled by bus bit BPS (bypass mode) and with a gain of 2. The bypass mode is not available for SECAM.

#### Comb filter interfacing