# AK3918 HD IP Camera SoC Specification

Version 1.0

# **Table of Contents**

| 1 Introduction                                                                                                                  | 5      |

|---------------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>1.1 Conventions</li> <li>1.2 Features</li> <li>1.3 Target Applications</li> <li>1.4 Product Decompositation</li> </ul> | 6<br>7 |

| 1.4 Product Documentation<br>1.5 Ordering Information                                                                           | 8      |

| 2 Signals and Connections                                                                                                       |        |

| 2.1 Pin Definitions<br>2.2 Shared-pin List                                                                                      | 20     |

| (Table 2-4 Shared-pin List)                                                                                                     |        |

| 3 Functional Description                                                                                                        |        |

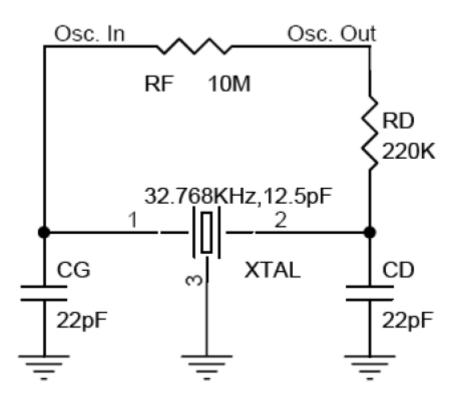

| 3.1 PMU<br>(Figure 3-1 PMU block diagram)                                                                                       |        |

| 3.1.1 Architecture                                                                                                              |        |

| 3.1.1.1 On-chip LDORTC                                                                                                          |        |

| 3.1.1.2 UVDET                                                                                                                   | 22     |

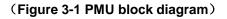

| 3.2 System Control<br>3.2.1 Clock Generation and Control                                                                        |        |

| (Figure 3-2 Clock Generation and Control)                                                                                       |        |

| 3.2.3 Interrupt Module                                                                                                          | 25     |

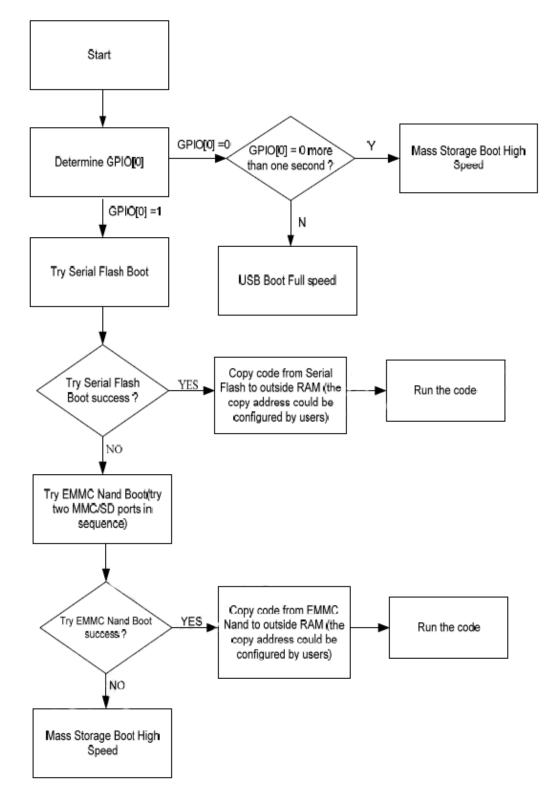

| 3.2.4 Bootstrap Module                                                                                                          | 25     |

| 3.2.5 Power Management Capability                                                                                               | 27     |

| 3.2.6 Working Modes                                                                                                             |        |

| 3.2.7 JTAG                                                                                                                      | 28     |

| 3.3 RTC Module                                                                                                                  | 28     |

| 3.4 CPU core                                                                                                                    |        |

| 3.5 Memory<br>3.5.1 On Chip Memory                                                                                              |        |

| 3.5.1.1 ROM                                                                                                                     |        |

| 3.5.1.2 L2 Memory                                                                                                               | 29     |

| 3.5.2 RAM Controller                                                                                                            |        |

| 3.6 CRC Module                                                                                                                  | 30     |

| 3.7 Advanced High-performance Bus (AHB)                                                                                         |        |

| 3.8 Register Bus Controller                                                                                                     |        |

| 3.9 I2S Interface                                                                                                               |        |

| 3.9.1 Typical Applications<br>3.9.1.1 Transmitter modes                                                                         |        |

|                                                                                                                                 |        |

| 3.9.1.2 Receiver Mode                      | 31 |

|--------------------------------------------|----|

| 3.10 Video Processor                       | 32 |

| 3.11 ISP Interface                         | 32 |

| 3.11.1 Timing                              |    |

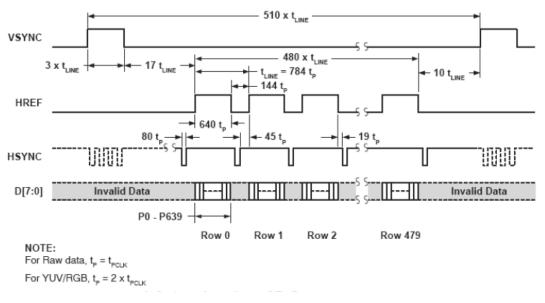

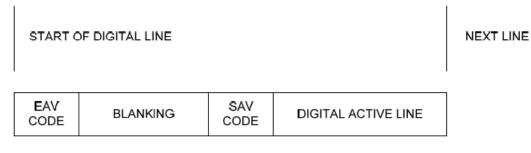

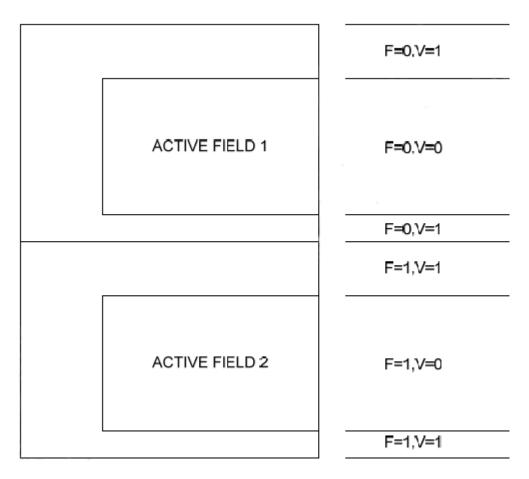

| 3.11.1.1 Bt601 Interface Timing            | 33 |

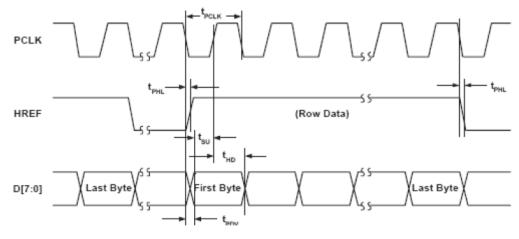

| 3.11.1.2 Bt656 Interface Timing            |    |

| 3.12 Encryption                            | 35 |

| 3.12.1 Features                            | 35 |

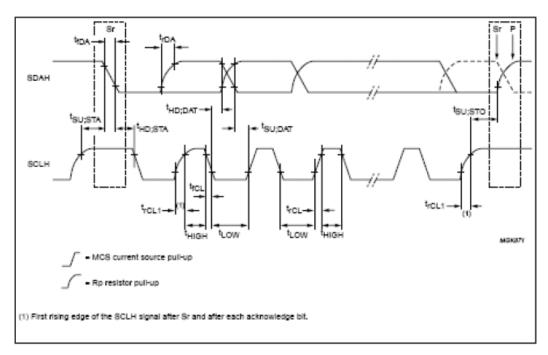

| 3.13 I2C Interface                         | 35 |

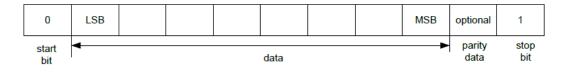

| 3.14 UART                                  | 36 |

| 3.15 IrDA                                  |    |

| 3.16 SPI                                   |    |

| 3.17 USB 2.0 HS Host and Slave Controllers |    |

| 3.18 MCI Interface                         |    |

| 3.19 Ethernet MAC                          | 41 |

| 3.20 Analog                                |    |

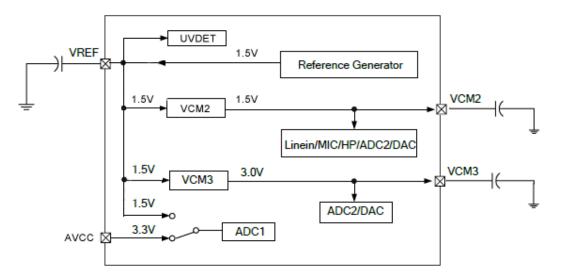

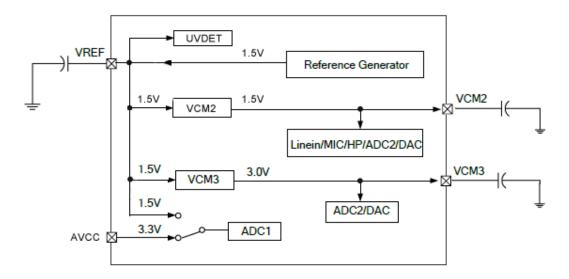

| 3.20.1 Reference Voltage Generator         | 42 |

| 3.20.2 Audio Codec                         | 42 |

| 3.20.2.1 ADC2                              | 43 |

| 3.20.2.1.1 Microphone Interface            | 43 |

| 3.20.2.1.2 Linein Interface                | 43 |

| 3.20.2.2 DACs                              | 43 |

| 3.20.2.2.1 Headphone Driver                | 43 |

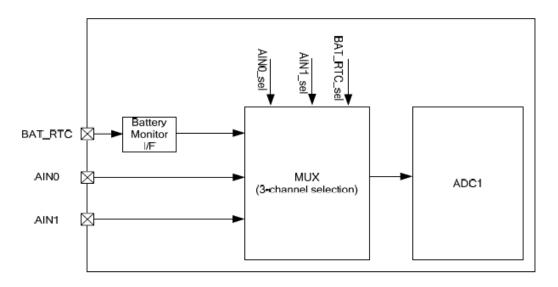

| 3.20.3 ADC1                                | 44 |

| 3.20.3.1 Battery Monitor                   | 44 |

| 3.20.3.2 AIN0 and AIN1 channels            | 44 |

| 3.21 PWM                                   | 45 |

| 3.22 Timers                                | 45 |

| 3.23 GPIO                                  | 45 |

| 4 Electrical Specifications                | 46 |

| 4.1 Maximum Ratings                        | 46 |

| 4.2 Recommended Operating Range            | 46 |

| 4.3 DC Electrical Characteristics          | 47 |

| 4.4 AC Electrical Characteristics          | 47 |

| 4.5 LDORTC Electrical Characteristics      | 48 |

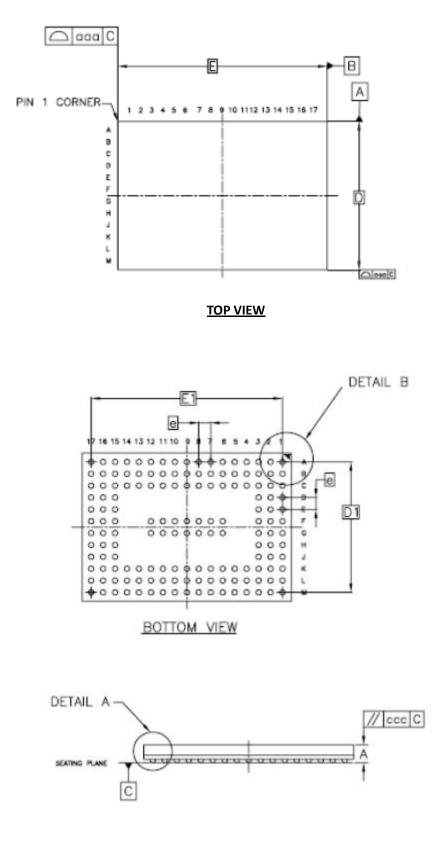

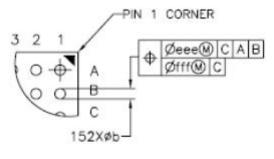

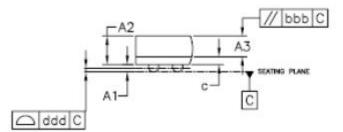

| 5.1 PIN Assignment                         | 48 |

| 5.2 Package Information                    | 51 |

| 6 Reflow Profile                           | 53 |

# **Document Revision History**

The following table provides revision history for this release. This history includes technical content revisions only and not stylistic or grammatical changes.

| VERSION | DESCRIPTION     | DATE COMPLETED |

|---------|-----------------|----------------|

| 1.0     | Initial release | July, 2014     |

# **About This Manual**

This document is the electrical and mechanical specification data sheet for the AK3918 processor. This specification contains a functional overview, mechanical data, package signal locations, electrical specifications (simulated), and bus functional waveforms.

# **Definitions, Acronyms, and Abbreviations**

Unless otherwise specified, all the acronyms and abbreviations used in this annual are defined hereunder.

ADC Analog to Digital Converter AHB Advanced High-performance Bus ASIC Application-Specific Integrated Circuit, refers to all the functional blocks of the processor CMOS Complimentary Metal-Oxide Semiconductor CRC Cyclic Redundancy Check DAC Digital to Analog Converter DDR **Double Data Rate** DMA **Direct Memory Access** DTE Data Terminal Equipment ECC **Error Correction Code FIFO** First In First Out GPIO General Purpose Input/Output I2C Inter-Integrated Circuit I2S Inter-IC Sound IrDA Infrared Data Association JPEG Joint Picture Expert Group JTAG Joint Test Action Group LSB Least Significant Bit MAC Media Access Control MMC Multimedia Card MMU Memory Management Unit MPEG Moving Picture Experts Group MSB Most Significant Bit PCM **Pulse Code Modulation** PGA Programmable Gain Amplifier PWM Pulse-Width Modulator PLL Phase Locked Loop RAM Random Access Memory ROM Read Only Memory RTC Real Time Clock SD Secure Digital SDRAM Synchronous Dynamic Random Access Memory SPI Serial Peripheral Interface SRAM Static Random Access Memory TBD To be determined UART Universal Asynchronous Receiver/Transmitter USB **Universal Serial Bus** XTAL Crystal

# **1Introduction**

Newly rolled out by Anyka, AK3918 is specially designed for cost-sensitive, low power and high performance HD IP Camera applications to meet the increasing surveillance requirements of high-definition videos.

With the embedded DDR2, H.264 hardware encoder, ISP, AES/DES/3DES encryption, high performance can be easily gained by AK3918. Rich peripheral interfaces, such as MAC,MMC/SD/SDIO, UART and USB HS Host/Slave are integrated in the SoC, thus bringing amore compact system with significant reduction of system cost for HD IP Camera applications.

For applications development on AK3918, a Product Development Kit with completely development platforms and reference designs are available for customers to develop specific applications with simplest structure in a most convenient way.

AK3918 functional block diagram is shown as follows.

(Figure 1-1 AK3918 Functional Block Diagram)

## **1.1 Conventions**

- #Abc is used to indicate a signal that is active when pulled low: for example, #Reset.

- Logic level one is a voltage that corresponds to Boolean true (1) state.

- Logic level zero is a voltage that corresponds to Boolean false (0) state.

- To set a bit or bits means to establish logic level one.

- To clear a bit or bits means to establish logic level zero.

• A signal is an electronic construct whose state conveys or changes in state convey information.

• A pin is an external physical connection. The same pin can be used to connect a number of signals.

- · Asserted means that a discrete signal is in active logic state.

- Negated means that an asserted discrete signal changes logic state.

- LSB means least significant bit or bits, and MSB means most significant bit or bits. References to low and high bytes or words are spelled out.

- Numbers ended in letter B are binary. Numbers preceded by 0x are hexadecimal.

## 1.2 Features

To support a wide variety of applications, AK3918 boasts a robust array of features, including the following:

- ARM926EJ core, 16KB I cache and 16KB D cache

- advanced power management module

- · supports little endian only

- Embedded 64MHz DDR2

- audio capability of MP3 encoder, ARM encoder, WAV encoder, Speex encoder

- MJPEG hardware encoder at 720p 30fps

- · Multi-Stream encoding synchronously

- H.264 hardware encoder at 720p 30fps

- CCIR 601/CCIR 656 CMOS image sensor interface with programmable image size and smart scaling capability

- Ethernet MAC controller

- · two ADCs for voice/music recording and battery measurement

- two Sigma-Delta DACs for stereo speakers

- · built-in headphone driver

- · I2S slave interface

- I2C master interface

- 2 UARTs, 1 has flow control

- IrDA (under NEC protocol)

- ISP

- AES/DES/3DES Encrytion

- 2 SPI (master or slave operation)

- MMC/SD interface. MMC 4.2; SD 2.0

- SDIO interface, Version 1.1

- USB 2.0 HS Host/Slave

- · 64 GPIOs, 7 dedicated, 57 shared with other pins

- JTAG supporting in-circuit debugging

- on-chip PLL and 32.768KHz RTC

- 5 PWMs

- 5 General Purpose timers

- 1 watchdog timer

- 1 RTC timer

- Four bootstrap modes, boot code saved in 32KB ROM

- package: 152-pin LFBGA

## **1.3 Target Applications**

The AK3918 is oriented at IP Camera and mobile surveillance equipments.

## **1.4 Product Documentation**

The following document(s) is (are) required for a complete description of the AK3918 and are necessary to design properly with the device.

AK3918 Specification

# **1.5 Ordering Information**

| PART NUMBER | PACKAGE      | OPERATING             | ORDER  |

|-------------|--------------|-----------------------|--------|

|             | TYPE         | VOLTAGE               | NUMBER |

| AK3918B152  | 152PIN-LFBGA | I/O: 3.3V, core: 1.2V |        |

# **2 Signals and Connections**

## **2.1 Pin Definitions**

Table 2-1 identifies and describes the AK3918 signals that are assigned to package pins.

I: input; O: output; IO: input/output; PWR: power supply; GND: ground; A: analog; D: digital.PU: pull-up; PD: pull-down.

| PIN | PIN NAME         | TYPE | RESET    | PIN MUX  | DESCRIPTION                         |

|-----|------------------|------|----------|----------|-------------------------------------|

| A1  | MIC_P            | I/A  | -        | MIC_P    | Positive input of microphone.       |

| A2  | MIC_N            | I/A  | -        | MIC_N    | Negative input of microphone.       |

| A3  | HPL              | O/A  | -        | HPL      | Left channel of Headphone output.   |

| A4  | HPR              | O/A  | -        | HPR      | Right channel of Headphone          |

|     |                  |      |          |          | output.                             |

| A5  | VCM3             | O/A  | -        | VCM3     | Third reference voltage (3.0V). To  |

|     |                  |      |          |          | filter out noise, it is recommended |

|     |                  |      |          |          | to connect to a                     |

|     |                  |      |          |          | 4.7uF or a 10uF capacitor and a     |

|     |                  |      |          |          | 0.1uF capacitor in parallel between |

|     |                  |      |          |          | the pin and the GND. This pin is    |

|     |                  |      |          |          | also used as the bias               |

|     |                  |      |          |          | voltage for microphone.             |

| A6  | BAT_RTC          | I/A  | -        | BAT_RTC  | 1. Battery voltage input for RTC    |

|     |                  |      |          |          | module.                             |

|     |                  |      |          |          | 2. Test mode signal. It must be     |

|     |                  |      |          |          | larger than 3V in normal working    |

|     |                  |      |          |          | state.                              |

| A7  | XTAL32KO         | O/D  | XTAL32KI | XTAL32KO | External 32.768KHz crystal output.  |

| A8  | XTAL32KI         | I/D  | -        | XTAL32KI | External 32.768KHz crystal input.   |

| A9  | GPIO[60]         | IO/D | I/PD     | GPIO[60] | GPIO[60]                            |

| A10 | GPIO[59]         | IO/D | I/PD     | GPIO[59] | GPIO[59]                            |

| A11 | GPIO[58]         | IO/D | I/PD     | GPIO[58] | GPIO[58]                            |

|     |                  |      | GPIO[56] | GPIO[56] | GPIO[56]                            |

| A12 | GPIO[56]/PWM5    | IO/D | I/PU     | PWM5     | Pulse-Width Modulated output        |

|     |                  |      | 1/1 0    |          | signal.                             |

| A13 | CIS_D[3]         | IO/D | I/PD     | CIS_D[3] | Camera pixel data input.            |

| A14 | CIS_D[2]         | IO/D | I/PD     | CIS_D[2] | Camera pixel data input.            |

| A15 | CIS_D[1]/GPIO[9] | IO/D | CIS_D[1] | CIS_D[1] | Camera pixel data input.            |

|     |                  | 10/0 | I/PD     | GPIO[9]  | GPIO[9]                             |

#### (Table 2-1 AK3918 Functional Pin Definitions)

| A16CIS_D[0]/GPI0[8]I/DI/DCIS_D[0]CIS_D[0]Care pixel data input.A17CIS_HSYNCI/DI/DI/PDCIS_HSYNCGPI0[8]GPI0[8]B1VREFI/DI/DI/PDCIS_HSYNCI/DI/SV reference voltage. It is recommended to connect to a 4.7UF capacitor between this pin and GND.B2VCM2O/A-VREFSecond reference voltage. It is recommended to connect to a 4.7UF capacitor between this pin and GND.B2VCM2O/A-VCM2Second reference voltage. It is recommended to connect to a 4.7UF capacitor between this pin and GND.B3Linein_RI/A-Linein_RRight channel of line in (AC coupling).B4AINOI/A-AINOAD input node, maybe used for analog keypad.B5#RSTI/DI/PU#RSTSystem reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.B6GPI0[57]/I2S_DINI/DI/PUI/PUGPI0[57]GPI0[50]B7GPI0[60]/PWM3I/DI/Ibigh-zGPI0[50]GPI0[50]B8GPI0[49]I/DI/Ibigh-zGPI0[4]GPI0[4]GPI0[4]B9GPI0[4]/TDI/RXD2/PWM1I/DI/Ibigh-zGPI0[4]GPI0[4]GPI0[4]B9GPI0[54]/12S_BCLKI/DGPI0[54]GPI0[54]GPI0[54]B10GPI0[54]/12S_BCLKI/DGPI0[54]GPI0[54]GPI0[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PIN | PIN NAME              | TYPE | RESET    | PIN MUX   | DESCRIPTION                   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------|------|----------|-----------|-------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

| A16       CIS_D[0]/GPI0[8]       IO/D       I/PD       GPI0[8]       GPI0[8]       GPI0[8]         A17       CIS_HSYNC       I/D       I/PD       CIS_HSYNC       Horizontal sync signal from camera.         B1       VREF       IO/A       -       VREF       I.5V reference voltage. It is recommended to connect to a 4.7uF capacitor between this pin and GND.         B2       VCM2       O/A       -       VCM2       Second reference voltage. (1.5V). To filter out noise, it is recommended to connect to a 4.7uF capacitor between the pin and the GND.         B3       Linein_R       I/A       -       VCM2       Second reference voltage. (1.5V). To filter out noise, it is recommended to connect to a 4.7uF or a 10uF capacitor and a 0.1ufcapacitor in parallel between the pin and the GND.         B3       Linein_R       I/A       -       Linein_R       Right channel of line in (AC coupling).         B4       AIN0       I/A       -       AIN0       AD input node, maybe used for analog keypad.         B5       #RST       I/D       I/PU       #RST       System reset, external active all modules (with the exception of RTC module) are reset.         B6       GPI0[57]/12S_DIN       IO/D       GPI0[57]       GPI0[57]       GPI0[50]         B7       GPI0[50]/PWM3       I/D       I/high-z       GPI0[50]       GPI0[50]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| A17     CIS_HSYNC     I/D     I/D     I/PD     CIS_HSYNC     Horizontal sync signal from camera.       B1     VREF     IO/A     -     VREF     Horizontal sync signal from camera.       B1     VREF     IO/A     -     VREF     I.5V reference voltage. It is recommended to connect to a 4.7UF capacitor between this pin and GND.       B2     VCM2     O/A     -     VCM2     VCM2     Second reference voltage (1.5V). To filter out noise, it is recommended to connect to a 4.7UF or a 10UF capacitor in parallel between the pin and the GND.       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC coupling).       B4     AINO     I/A     -     AINO     AD input node, maybe used for analog keypad.       B5     #RST     I/D     I/PU     #RST     System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.       B6     GPIO[57]/I2S_DIN     IO/D     GPIO[57]     GPIO[50]     GPIO[50]       B7     GPIO[50]/PWM3     IO/D     GPIO[57]     GPIO[50]     GPIO[50]     GPIO[50]       B8     GPIO[49]     I/D     I/high-z     GPIO[49]     GPIO[49]     GPIO[49]       B9     GPIO[4]/TDI/RXD2/PWM1     IO/D     GPIO[4]     GPIO[4]     GPIO[4]       B9 <td>A16</td> <td>CIS_D[0]/GPIO[8]</td> <td>IO/D</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A16 | CIS_D[0]/GPIO[8]      | IO/D |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| A17     CIS_HSYNC     I/D     I/PD     CIS_HSYNC     camera.       B1     VREF     IO/A     -     VREF     1.5V reference voltage. It is recommended to connect to a 4.7U capacitor between this pin and GND.       B2     VCM2     O/A     -     VCM2     Second reference voltage (1.5V). To filter out noise, it is recommended to connect to a 4.7UF capacitor between the pin and GND.       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC coupling).       B4     AIN0     I/A     -     Linein_R     Right channel of line in (AC coupling).       B4     AIN0     I/A     -     AIN0     A/D input node, maybe used for analog keypad.       B5     #RST     I/D     I/PU     #RST     System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.       B6     GPIO[57]/I2S_DIN     IO/D     GPI0[50]     GPI0[57]     GPI0[57]       B7     GPI0[60]/PWM3     IO/D     GPI0[50]     GPI0[50]     PWM3     Pulse-Width Modulated output signal.       B8     GPI0[4]     I/D     I/high-z     GPI0[4]     GPI0[4]     GPI0[4]       B9     GPI0[4]/TDI/RXD2/PWM1     IO/D     GPI0[50]     Fulse-Width Modulated output signal.       B10     GPI0[54]/I2S_BCLK     IO/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B1     VREF     IO/A     -     VREF     I.5V reference voltage. It is recommended to connect to a 4.7UF capacitor between this pin and GND.       B2     VCM2     O/A     -     VREF     VCM2     Second reference voltage (1.5V). To filter out noise, it is recommended to connect to a 4.7UF capacitor and a 0.1ufcapacitor in parallel between the pin and the GND.       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC coupling).       B4     AIN0     I/A     -     Linein_R     Right channel of line in (AC coupling).       B4     AIN0     I/A     -     AIN0     A/D input node, maybe used for analog keypad.       B5     #RST     I/D     I/PU     #RST     System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.       B6     GPIO[57]/I2S_DIN     IO/D     GPIO[57]     GPIO[57]     GPIO[57]       B7     GPIO[50]/PWM3     IO/D     GPIO[57]     GPIO[57]     GPIO[57]       B8     GPIO[4]/IDI/RXD2/PWM1     IO/D     GPIO[57]     GPIO[57]     GPIO[57]       B9     GPIO[4]/TDI/RXD2/PWM1     IO/D     GPIO[57]     GPIO[4]     GPIO[4]     GPIO[4]       B10     GPIO[54]/I2S_BCLK     IO/D     GPIO[54]     GPIO[54]     GPIO[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A17 | CIS_HSYNC             | I/D  | I/PD     | CIS_HSYNC |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B1     VREF     IO/A     -     VREF     recommended to connect to<br>a 4.7uF capacitor between<br>this pin and GND.       B2     VCM2     O/A     -     VCM2     Second reference voltage<br>(1.5V). To filter out noise, it<br>is recommended to connect<br>to a       B2     VCM2     O/A     -     VCM2     Second reference voltage<br>(1.5V). To filter out noise, it<br>is recommended to connect<br>to a       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC<br>coupling).       B4     AIN0     I/A     -     AIN0     A/D input node, maybe<br>used for analog keypad.       B5     #RST     I/D     I/PU     #RST     System reset, external<br>active low. Schmitt trigger<br>input signal. When this<br>signal is active, all modules<br>(with the exception of RTC<br>module) are reset.       B6     GPI0[57]/I2S_DIN     IO/D     GPI0[57]     GPI0[50]     GPI0[57]       B7     GPI0[50]/PWM3     IO/D     GPI0[50]     GPI0[50]     GPI0[50]       B8     GPI0[49]     I/D     I/high-z     GPI0[61]     GPI0[40]     GPI0 used for USB pull<br>in/out detection.       B9     GPI0[4]/TDI/RXD2/PWM1     I/D     GPI0[51]     GPI0[4]     GPI0[4]     GPI0[4]       B910     GPI0[54]/I2S_BCLK     IO/D     GPI0[54]     GPI0[54]     Fulse-Width Modulated<br>output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B1     VREF     IO/A     -     VREF     a 4.7uF capacitor between this pin and GND.       B2     VCM2     O/A     -     VCM2     Second reference voltage (1.5V). To filter out noise, it is recommended to connect to a 4.7uF or a 10uF capacitor in parallel between the pin and the GND.       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC coupling).       B4     AINO     I/A     -     AINO     AINO     Right channel of line in (AC coupling).       B5     #RST     I/D     I/PU     #RST     System reset, external active low. Schnitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.       B6     GPI0[57]/12S_DIN     IO/D     GPI0[57]     GPI0[50]     GPI0[50]       B7     GPI0[50]/PWM3     IO/D     GPI0[50]     GPI0[50]     GPI0[50]       B8     GPI0[49]     I/D     I/high-z     GPI0[60]     GPI0[50]     GPI0[4]       B9     GPI0[4]/TDI/RXD2/PWM1     IO/D     GPI0[4]     GPI0[4]     GPI0[4]     GPI0[4]       B10     GPI0[54]/[2S_BCLK     IO/D     GPI0[54]     GPI0[54]     GPI0[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B2       VCM2       O/A       -       VCM2       Second reference voltage (1.5V). To filter out noise, it is recommended to connect to a 4.7uF or a 10uF capacitor in parallel between the pin and the GND.         B3       Linein_R       I/A       -       Linein_R       Right channel of line in (AC coupling).         B4       AINO       I/A       -       Linein_R       Right channel of line in (AC coupling).         B4       AINO       I/A       -       AINO       A/D input node, maybe used for analog keypad.         B5       #RST       I/D       I/PU       #RST       System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.         B6       GPIO[57]/I2S_DIN       IO/D       GPIO[57]       GPIO[57]       GPIO[57]         B7       GPIO[50]/PWM3       IO/D       GPIO[51]       I2S_DIN       I2S serial data input.         B8       GPIO[49]       I/D       I/high-z       GPIO[50]       GPIO[50]         B8       GPIO[49]       I/D       I/high-z       GPIO[4]       GPIO[4]       GPIO[4]         B9       GPIO[4]/TDI/RXD2/PWM1       IO/D       GPIO[4]       GPIO[4]       GPIO[4]       GPIO[4]       GPIO[4]       GPIO[4]         B9       GPIO[4]/TDI/RXD2/PWM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B1  | VREF                  | IO/A | -        | VREF      |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B2     VCM2     O/A     -     VCM2     Second reference voltage<br>(1.5V). To filter out noise, it<br>is recommended to connect<br>to a<br>4.7uF or a 10uF capacitor<br>and a 0.1ufcapacitor in<br>parallel between the pin and<br>the GND.       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC<br>coupling).       B4     AIN0     I/A     -     AIN0     AD input node, maybe<br>used for analog keypad.       B5     #RST     I/D     I/PU     #RST     System reset, external<br>active low. Schmitt trigger<br>input signal. When this<br>signal is active, all modules<br>(with the exception of RTC<br>module) are reset.       B6     GPI0[57]/12S_DIN     IO/D     GPI0[57]<br>I/PU     GPI0[57]     GPI0[57]       B7     GPI0[50]/PWM3     IO/D     GPI0[50]<br>I/PU     GPI0[50]     GPI0[50]       B8     GPI0[49]     I/D     I/high-z     GPI0[49]     GPI0[49]       B8     GPI0[49]     I/D     I/high-z     GPI0[4]     GPI0[4]       B9     GPI0[4]/TDI/RXD2/PWM1     IO/D     GPI0[4]     GPI0[4]     GPI0[4]       B10     GPI0[54]/[2S_BCLK     IO/D     GPI0[54]     GPI0[54]     GPI0[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B2     VCM2     O/A     -     Image: VCM2     Image: VCM2 </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B2     VCM2     O/A     -     VCM2     is recommended to connect<br>to a<br>4.7uF or a 10uF capacitor<br>and a 0.1ufcapacitor in<br>parallel between the pin and<br>the GND.       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC<br>coupling).       B4     AIN0     I/A     -     AIN0     A/D     AUN0       B5     #RST     I/D     I/A     -     AIN0     A/D on analog keypad.       B6     GPI0[57]/12S_DIN     I/D     I/PU     #RST     System reset, external<br>active low. Schmitt trigger<br>input signal. When this<br>signal is active, all modules<br>(with the exception of RTC<br>module) are reset.       B6     GPI0[57]/12S_DIN     IO/D     GPI0[57]     GPI0[57]     GPI0[57]       B7     GPI0[50]/PWM3     IO/D     GPI0[57]     GPI0[50]     PUIse-Width Modulated<br>output signal.       B8     GPI0[4]     I/D     I/high-z     GPI0[4]     GPI0[4]     GPI0[4]       B9     GPI0[4]/TDI/RXD2/PWM1     IO/D     GPI0[4]     GPI0[4]     GPI0[4]       B10     GPI0[54]/I2S_BCLK     IO/D     GPI0[54]     GPI0[54]     PUSe-Width Modulated<br>output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                       |      |          |           | -                             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B2     VCM2     O/A     -     VCM2     to a<br>4.7uF or a 10uF capacitor<br>and a 0.1ufcapacitor in<br>parallel between the pin and<br>the GND.       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC<br>couping).       B4     AINO     I/A     -     AINO     AINO     AU       B5     #RST     I/A     -     AINO     AU     AUD input node, maybe<br>used for analog keypad.       B6     GPI0[57]/12S_DIN     I/D     I/PU     #RST     System reset, external<br>active low. Schmitt trigger<br>input signal. When this<br>signal is active, all modules<br>(with the exception of RTC<br>module) are reset.       B6     GPI0[57]/12S_DIN     IO/D     GPI0[57]<br>I/PU     GPI0[57]     GPI0[57]       B7     GPI0[50]/PWM3     IO/D     GPI0[50]<br>I/PU     GPI0[50]     GPI0[50]       B8     GPI0[49]     I/D     I/high-z     GPI0[49]     GPI0[49]     GPI0[49]       B9     GPI0[4]/TDI/RXD2/PWM1     IO/D     GPI0[4]<br>I/PU     GPI0[4]     GPI0[4]     GPI0[4]       B10     GPI0[54]/I2S_BCLK     IO/D     GPI0[54]     GPI0[54]     GPI0[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B2     VCM2     O/A     -     VCM2     4.7uF or a 10uF capacitor<br>and a 0.1ufcapacitor in<br>parallel between the pin and<br>the GND.       B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC<br>coupling).       B4     AINO     I/A     -     AINO     A/D input node, maybe<br>used for analog keypad.       B5     #RST     I/A     -     AINO     A/D input node, maybe<br>used for analog keypad.       B5     #RST     I/D     I/PU     #RST     System reset, external<br>active low. Schmitt trigger<br>input signal. When this<br>signal is active, all modules<br>(with the exception of RTC<br>module) are reset.       B6     GPIO[57]/12S_DIN     IO/D     GPI0[57]<br>I/PU     GPI0[57]     GPI0[57]       B7     GPI0[50]/PWM3     IO/D     GPI0[50]<br>I/PU     GPI0[50]     Pulse-Width Modulated<br>output signal.       B8     GPI0[49]     I/D     I/high-z     GPI0[49]     GPI0[49] is a dedicated<br>GPI0[49] is a dedicated<br>GPI0[41]       B8     GPI0[41]/TDI/RXD2/PWM1     IO/D     GPI0[41]/TDI     GPI0[41]     GPI0[41]       B9     GPI0[41/TDI/RXD2/PWM1     IO/D     GPI0[41]     GPI0[41]     GPI0[41]     GPI0[41]       B10     GPI0[541//12S_BCLK     IO/D     GPI0[541]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B3         Linein_R         I/A         -         Linein_R         Right channel of line in (AC coupling).           B4         AINO         I/A         -         Linein_R         Right channel of line in (AC coupling).           B4         AINO         I/A         -         AINO         A/D input node, maybe used for analog keypad.           B5         #RST         I/A         -         AINO         System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.           B6         GPIO[57]/I2S_DIN         IO/D         GPIO[57]         GPIO[57]         GPIO[57]           B7         GPIO[50]/PWM3         IO/D         GPIO[50]         GPIO[50]         PUIse-Width Modulated output signal.           B8         GPIO[49]         I/D         I/high-z         GPIO[49]         GPIO[49]         GPIO[49]         GPIO[49] is a dedicated output signal.           B8         GPIO[49]         I/D         I/high-z         GPIO[49]         GPIO[49] is a dedicated output signal.           B9         GPIO[4]/TDI/RXD2/PWM1         IO/D         GPIO[4]         GPIO[4]         GPIO[4]           B9         GPIO[4]/TDI/RXD2/PWM1         I/D         I/high-z         GPIO[4]         GPIO[4]         GPIO[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B2  | VCM2                  | O/A  | -        | VCM2      |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B3     Linein_R     I/A     -     Linein_R     Right channel of line in (AC coupling).       B4     AINO     I/A     -     AINO     A/D input node, maybe used for analog keypad.       B4     AINO     I/A     -     AINO     A/D input node, maybe used for analog keypad.       B5     #RST     I/D     I/A     -     AINO     A/D input node, maybe used for analog keypad.       B6     #RST     I/D     I/PU     #RST     System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.       B6     GPIO[57]/I2S_DIN     IO/D     GPI0[57]     GPI0[57]     GPI0[57]       B7     GPI0[50]/PWM3     IO/D     GPI0[50]     PWM3     Pulse-Width Modulated output signal.       B8     GPI0[49]     I/D     I/high-z     GPI0[49]     GPI0[49]     GPI0[49]       B9     GPI0[4]/TDI/RXD2/PWM1     IO/D     GPI0[4]     GPI0[4]     GPI0[4]     GPI0[4]       B10     GPI0[54]/I2S BCLK     IO/D     GPI0[64]     GPI0[4]     GPI0[4]     Fulse-Width Modulated output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                       |      |          |           | ·                             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| Image: Base of the constraint of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B3       Linein_R       I/A       -       Linein_R       Right channel of line in (AC coupling).         B4       AINO       I/A       -       AINO       AVD input node, maybe used for analog keypad.         B5       #RST       I/D       I/PU       AINO       System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.         B6       GPI0[57]/I2S_DIN       IO/D       GPI0[57]       GPI0[57]       GPI0[57]         B7       GPI0[50]/PWM3       IO/D       GPI0[50]       GPI0[50]       GPI0[50]         B8       GPI0[4]       I/D       I/high-z       GPI0[6]       GPI0[4]       GPI0 used for USB pull in/out detection.         B8       GPI0[4]/TDI/RXD2/PWM1       IO/D       I/high-z       GPI0[4]       GPI0[4]       GPI0[4]         B9       GPI0[4]/TDI/RXD2/PWM1       I/D       I/high-z       GPI0[4]       GPI0[4]       GPI0[4]         B10       GPI0[54]/I2S_BCLK       IO/D       GPI0[54]       GPI0[54]       GPI0[54]       GPI0[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B3     Linein_R     I/A     -     Linein_R     coupling).       B4     AINO     I/A     -     AINO     A/D input node, maybe<br>used for analog keypad.       B4     AINO     I/A     -     AINO     A/D input node, maybe<br>used for analog keypad.       B5     #RST     I/D     I/PU     AINO     System reset, external<br>active low. Schmitt trigger<br>input signal. When this<br>signal is active, all modules<br>(with the exception of RTC<br>module) are reset.       B6     GPIO[57]/I2S_DIN     IO/D     GPIO[57]<br>I/PU     GPIO[57]     GPIO[57]       B7     GPIO[50]/PWM3     IO/D     GPIO[50]<br>I/PU     GPIO[50]     GPIO[50]       B8     GPIO[49]     I/D     I/high-z     GPIO[49]     PWM3     GPIO[49]       B8     GPIO[4]     I/D     I/high-z     GPIO[49]     GPIO[49]     GPIO[49]       B9     GPIO[4]/TDI/RXD2/PWM1     IO/D     GPIO[4]     GPIO[4]     GPIO[4]     GPIO[4]       B9     GPIO[4]/TDI/RXD2/PWM1     IO/D     GPIO[4]     GPIO[4]     GPIO[4]     GPIO[4]       B10     GPIO[54]/I2S BCLK     IO/D     GPIO[54]     GPIO[54]     PUse-Width Modulated<br>output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B4     AINO     I/A     -     AINO     A/D input node, maybe<br>used for analog keypad.       B5     #RST     I/D     I/PU     IVPU     IVPU     System reset, external<br>active low. Schmitt trigger<br>input signal. When this<br>signal is active, all modules<br>(with the exception of RTC<br>module) are reset.       B6     GPIO[57]/I2S_DIN     IO/D     GPIO[57]<br>I/PU     GPIO[57]     GPIO[57]       B7     GPIO[50]/PWM3     IO/D     GPIO[50]<br>I/PU     GPIO[50]     GPIO[50]       B8     GPIO[50]/PWM3     IO/D     GPIO[50]<br>I/PU     GPIO[50]     GPIO[50]       B8     GPIO[49]     I/D     I/high-z     GPIO[49]     GPIO[49]     GPIO used for USB pull<br>in/out detection.       B9     GPIO[4]/TDI/RXD2/PWM1     IO/D     IO/D     GPIO[4]/I/PU     GPIO[4]     GPIO[4]       B10     GPIO[54]/I2S BCLK     IO/D     GPIO[54]     GPIO[54]     GPIO[54]     GPIO[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | B3  | Linein_R              | I/A  | -        | Linein_R  | -                             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B4     AINO     I/A     AINO     used for analog keypad.       B5     #RST     I/D     I/PU     AINO     used for analog keypad.       B5     #RST     I/D     I/PU     #RST     System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.       B6     GPIO[57]/I2S_DIN     IO/D     GPIO[57]     GPIO[57]     GPIO[57]       B7     GPIO[50]/PWM3     IO/D     GPIO[50]     GPIO[50]     GPIO[50]       B8     GPIO[49]     I/D     I/high-z     GPIO[49]     GPIO[49]     GPIO[49]       B8     GPIO[4]/TDI/RXD2/PWM1     IO/D     I/high-z     GPIO[4]     GPIO[4]     GPIO[4]       B9     GPIO[4]/TDI/RXD2/PWM1     IO/D     GPIO[4]     GPIO[4]     GPIO[4]     GPIO[4]       B10     GPI0[54]/I2S_BCLK     IO/D     GPIO[54]     GPIO[54]     GPIO[54]     GPIO[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

| B5     #RST     I/D     I/PU     #RST     System reset, external active low. Schmitt trigger input signal. When this signal is active, all modules (with the exception of RTC module) are reset.       B6     GPI0[57]/I2S_DIN     IO/D     GPI0[57]     GPI0[57]     GPI0[57]       B7     GPI0[50]/PWM3     IO/D     GPI0[50]     ISE     GPI0[50]       B7     GPI0[50]/PWM3     IO/D     GPI0[50]     GPI0[50]     GPI0[50]       B8     GPI0[50]/PWM3     IO/D     GPI0[50]     GPI0[50]     Pulse-Width Modulated output signal.       B8     GPI0[49]     I/D     I/high-z     GPI0[49]     GPI0[49]     GPI0[49]       B9     GPI0[4]/TDI/RXD2/PWM1     IO/D     IO/D     GPI0[4]     GPI0[4]     GPI0[4]       B9     GPI0[4]/TDI/RXD2/PWM1     IO/D     GPI0[4]     GPI0[4]     GPI0[4]       B10     GPI0[54]/I2S BCLK     IO/D     GPI0[54]     GPI0[54]     GPI0[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B4  | AINO                  | I/A  | -        | AIN0      |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |

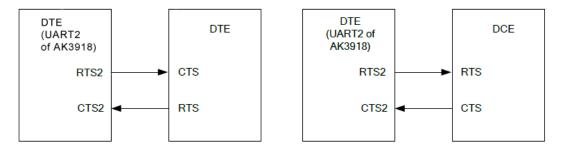

| B5#RSTI/DI/DI/PU#RSTactive low. Schmitt trigger<br>input signal. When this<br>signal is active, all modules<br>(with the exception of RTC<br>module) are reset.B6GPI0[57]/I2S_DINIO/DGPI0[57]GPI0[57]GPI0[57]B7GPI0[50]/PWM3IO/DGPI0[50]GPI0[50]ISS serial data input.B7GPI0[50]/PWM3IO/DGPI0[50]ISS serial data input.B8GPI0[50]/PWM3IO/DGPI0[50]PWM3Pulse-Width Modulated<br>output signal.B8GPI0[49]I/DI/high-zGPI0[49]GPI0 [49] is a dedicated<br>GPI0[49]B9GPI0[4]/TDI/RXD2/PWM1IO/DI/high-zGPI0[4]GPI0[4]B10GPI0[54]/TDI/RXD2/PWM1IO/DGPI0[54]TDIDebug port serial data input.B10GPI0[54]/I2S BCLKIO/DGPI0[54]GPI0[54]GPI0[54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |                       |      |          |           |                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |