# Battery Protection IC For 3-5 Cells Battery Pack With Automatic Balance

Parameters Subject to Change Without Notice

#### **DESCRIPTION**

JW<sup>®</sup>3312 is a battery protection IC for the3~5cellsrechargeable lithium-ion battery pack.By using cascadeconnection, it is also possible to protect 6 or more cells battery pack. JW3312integrates high-accuracy voltage detection circuits. which realizes multiple protection functions including overcharge, overdischarge, overcurrent, over-temperature and VC5~VC0 pins open-wire.

#### **FEATURES**

- Input voltage is high to 40V

- Monitor 3~5 series battery pack

- High-accuracy voltage detection for each cell Overcharge detection voltage:

3.55~4.6V (50mV step) Accuracy ±20 mV (-40 °C ~85 °C) Accuracy ±30 mV

Overcharge release hysteresis:

0V/0.1~0.4V (20mV step)

Overdischarge detection voltage:

2.0~3.2V (50mV step) Accuracy ±80 mV

Overdischarge release hysteresis:

0V/0.1~1V (60mV step)

- Discharge overcurrent detection in 3-step 1<sup>st</sup> Discharge overcurrent detection voltage: 0.025~0.25V (15mV step) Accuracy ±10mV 2<sup>nd</sup> Discharge overcurrent detection voltage: 0.05~0.5V (15mV step) Accuracy ±10mV Short circuit detection voltage:

0.1~1.6V (100mV step) Accuracy ±40mV

Company's Logo is Protected, "JW" and "JOULWATT" are Registered Trademarks of JoulWatt technology Inc.

- Charge overcurrent detection voltage

-0.015~-0.160V (10mV step) Accuracy ±10mV

- Fixed internally:

Load short circuit detection delay time

100us, 200us, 300us,400us optional

Charge overcurrent detection delay time

0.1s, 1s optional

- Programmable by external capacitor:

Discharge overcurrent detection delay time,

1<sup>st</sup>: 0.1s~2s 2<sup>nd</sup>: (0.1~2s)×0.1

Overdischarge detectiondelay time,

0.1s~3s

Overcharge detection delay time

0.1s~5s

- High-accuracy battery temperature detection

- Provide passive balance

- Provide VC5~VC0 open-wire detection

- Wide range of operation voltage4.5V to 35V

- Wide range of operation temperature

-40°C to +85°C

- Low current consumption (T=25°C)

During full power 15µA. (From chip GND)

During sleep mode 2µA.

During shutdown 350nA.

- 20-Pin TSSOP

### **APPLICATIONS**

- Rechargeable lithium-ion battery pack

- Power tool

- UPS backup battery

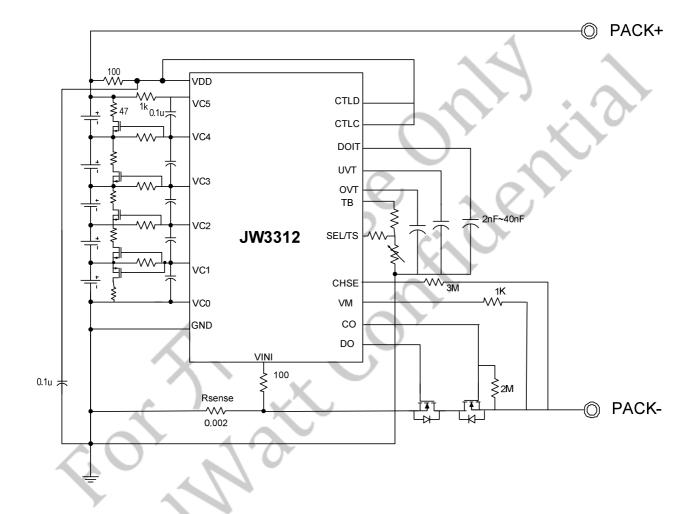

# **TYPICAL APPLICATION**

One PACK-PORT

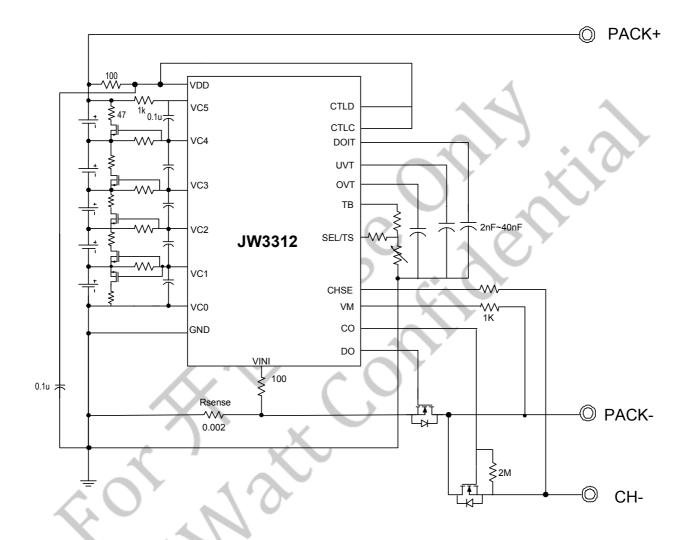

# **TYPICAL APPLICATION**

# PACK- CHG- separated

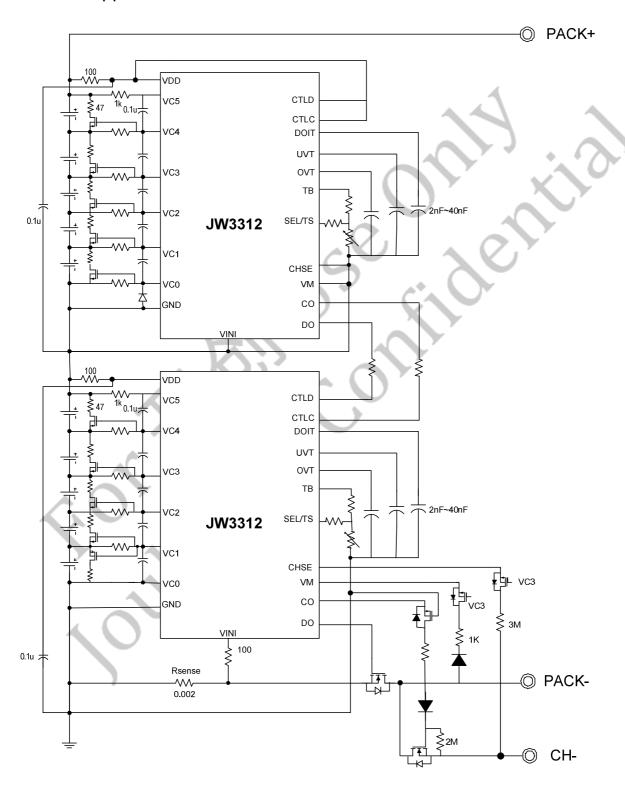

# **TYPICAL APPLICATION**

# Cascade application

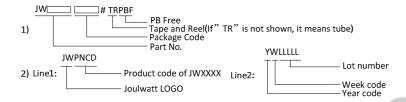

# ORDER INFORMATION

| DEVICE <sup>1)</sup> | PACKAGE | TOP MARKING <sup>2)</sup> |

|----------------------|---------|---------------------------|

| JW3312TSSOPE#TRPBF   | JW3312  |                           |

| JVV3312133UPE#1KPBF  | TSSOP20 | YWLLLL                    |

#### Notes:

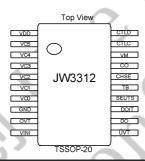

# **PIN CONFIGURATION**

# **ABSOLUTE MAXIMUM RATING<sup>1)</sup>**

| VDD,VC5,VC4,VC3,VC2,CHSE,            |                        |

|--------------------------------------|------------------------|

| VC1                                  | 0.3V to +20V           |

| VC0                                  | 0.3V to +6V            |

| CTLD,CTLC                            | 0.3Vto VDD+0.7V        |

| DO                                   | 0.3V to +12V           |

| CO, VM                               | Max(-18,VDD-40) to VDD |

| UVT, SEL/TS,DOIT,VINI, OVT, TB       |                        |

| Battery cell voltage                 | 0.3V to 24V            |

| Junction Temperature <sup>2)3)</sup> | 150°C                  |

| Lead Temperature                     | 260°C                  |

| Storage Temperature                  |                        |

|                                      |                        |

# RECOMMENDED OPERATING CONDITIONS

| Junction Temperature | (T <sub>J</sub> ) | -40°C to 125°C |

|----------------------|-------------------|----------------|

|----------------------|-------------------|----------------|

# THERMAL PERFORMANCE<sup>4)</sup>

|         | - UA  | - <i>0</i> C |

|---------|-------|--------------|

| TSSOP20 | .98.4 | 37°C/W       |

$\theta_{\mu}$   $\theta_{\nu}$

#### Note:

- 1) Exceeding these ratings may damage the device.

- 2) The JW3312guarantees robust performance from -40°Cto 150°C junction temperature. The junction temperature range specification is assured by design, characterization and correlation with statistical process controls.

- 3) Continuous operation over the specified absolutemaximum operating junction temperature may damagethe device.

- 4) Measured on JESD51-7, 4-layer PCB

# **ELECTRICAL CHARACTERISTICS**

| TA = 25°C, unless otherwise stated.                           |                                          |                          |                        |                         |                        |                 |

|---------------------------------------------------------------|------------------------------------------|--------------------------|------------------------|-------------------------|------------------------|-----------------|

| Item                                                          | Symbol                                   | Condition                | Min.                   | Тур.                    | Max. U                 | nits            |

| Power supply                                                  |                                          |                          |                        |                         |                        |                 |

| Operation voltage betweenVDD pin and GND pin                  | $V_{DSOP}$                               |                          | 4.5                    | ×                       | 35                     | >               |

| Power-on reset threshold                                      | V <sub>PON</sub>                         |                          | 1                      | V <sub>PDOWN</sub> +0.3 |                        | ٧               |

| Shutdown threshold                                            | V <sub>PDOWN</sub>                       | V <sub>PDOWN</sub> = 4.5 | V <sub>PDOWN</sub> -6% | V <sub>PDOWN</sub>      | V <sub>PDOWN</sub> +6% | V               |

| Current consumption during full power                         | I <sub>FP</sub>                          |                          | 2                      | 15                      |                        | μΑ              |

| Current consumption during sleep                              | I <sub>SLEEP</sub>                       | 0.                       |                        | 2                       | ,                      | μА              |

| Current consumption during shutdown                           | I <sub>SHUTDOWN</sub>                    | 5                        | 2                      | 350                     |                        | nA              |

| Voltage/Current Protections The                               | eshold Volta                             | age                      |                        |                         |                        |                 |

| Overcharge detection voltage                                  | Voc                                      |                          | V <sub>OC</sub> -0.02  | Voc                     | V <sub>OC</sub> +0.02  | V               |

| Overcharge release voltage                                    | V <sub>OCL</sub>                         |                          |                        | V <sub>ocl</sub>        |                        | ٧               |

| Overdischarge detection voltage                               | $V_{OD}$                                 |                          | V <sub>OD</sub> -0.08  | V <sub>OD</sub>         | V <sub>OD</sub> +0.08  | ٧               |

| Overdischarge release voltage <sup>5</sup>                    | $V_{ODH}$                                | ),                       |                        | $V_{ODH}$               |                        | V               |

| 1 <sup>st</sup> Discharge overcurrent detection voltage       | V <sub>DOI1</sub>                        |                          | V <sub>DOI1</sub> -10  | V <sub>DOI1</sub>       | V <sub>DOI1</sub> +10  | mV              |

| 2 <sup>nd</sup> Discharge overcurrent detection voltage       | $V_{DOI2}$                               |                          | V <sub>DOI2</sub> -10  | $V_{DOI2}$              | V <sub>DOI2</sub> +10  | mV              |

| Load short circuit detection voltage                          | V <sub>SHT</sub>                         |                          | V <sub>SHT</sub> -40   | $V_{SHT}$               | V <sub>SHT</sub> +40   | mV              |

| Charge overcurrent detection voltage                          | V <sub>col</sub>                         | T=-40°C to 85 °C         | V <sub>COI</sub> -10   | V <sub>COI</sub>        | V <sub>COI</sub> +10   |                 |

| Discharge detection threshold                                 | V <sub>TH_DSG</sub>                      |                          | 2.5                    | 4                       | 7.5                    | mV              |

| Temperature Protection Threshol                               | Temperature Protection Threshold Voltage |                          |                        |                         |                        |                 |

| Discharging detection threshold                               | V <sub>TH_DSG</sub>                      |                          | 2.5                    | 4                       | 7.5                    | mV              |

| Charging over temperature protection threshold                | V <sub>СОТ</sub>                         |                          | 28.58%                 | 29.58%                  | 30.58%                 | V <sub>TB</sub> |

| Charging over temperature protection hysteresis <sup>5)</sup> | V <sub>сотн</sub>                        |                          |                        | 3.33%                   |                        | $V_{TB}$        |

| Discharging over temperature protection threshold             | V <sub>DOT</sub>                         |                          | 17.33%                 | 18.33%                  | 19.33%                 | V <sub>TB</sub> |

|                                                                                    |                    |                        | Ι                     | I                |                       |                 |

|------------------------------------------------------------------------------------|--------------------|------------------------|-----------------------|------------------|-----------------------|-----------------|

| Discharging over temperature protection hysteresis <sup>5</sup>                    | $V_{DOTH}$         |                        |                       | 5%               |                       | V <sub>TB</sub> |

| Charging under temperature protection threshold                                    | V <sub>CUT</sub>   |                        | 72.33%                | 73.33%           | 74.33%                | V <sub>TB</sub> |

| Charging under temperature protection hysteresis <sup>5</sup>                      | V <sub>ситн</sub>  |                        |                       | 4.58%            |                       | V <sub>TB</sub> |

| Discharging under temperature protection threshold                                 | $V_{DUT}$          |                        | 86.08%                | 87.08%           | 88.08%                | V <sub>TB</sub> |

| Discharging under temperature protection hysteresis <sup>5</sup>                   | $V_{DUTH}$         |                        |                       | 6.25%            | . 0                   | $V_{TB}$        |

| Chip over temperature protection threshold <sup>5)</sup>                           | Т <sub>СНІР</sub>  |                        |                       | 150              |                       | °C              |

| Chip over temperature protection release threshold <sup>5)</sup>                   | $T_{CHIPR}$        | 0                      |                       | 125              |                       | °C              |

| Voltage/Current Protections Del                                                    | lay Time           |                        |                       |                  |                       |                 |

| Detection period time for OV, UV                                                   | t <sub>DETV</sub>  |                        |                       | 0.5              |                       | S               |

| Overcharge detection delay time                                                    | t <sub>oc</sub>    | (                      | t <sub>OC</sub> -25%  | toc              | t <sub>OC</sub> +25%  | S               |

| Overdischarge detection delay time                                                 | t <sub>od</sub>    |                        | t <sub>OD</sub> -25%  | t <sub>OD</sub>  | t <sub>OD</sub> +25%  | S               |

| Load short circuit detection delay time                                            | t <sub>sнт</sub>   | (0)                    | t <sub>SHT</sub> -150 | t <sub>sнт</sub> | t <sub>SHT</sub> +150 | μS              |

| DOIT/UVT pin current                                                               | I <sub>DOIT</sub>  |                        | 7.7                   | 8                | 8.3                   | μΑ              |

| 1 <sup>st</sup> Discharge overcurrrentdetection delay time                         | t <sub>DOI1</sub>  | C <sub>DOIT</sub> =2nF | 0.07                  | 0.1              | 0.13                  | S               |

| DOIT pin short detected 1 <sup>st</sup> discharge overcurrent detection delay time | t <sub>DOI1S</sub> |                        | 1.4                   | 2                | 2.6                   | S               |

| DOIT pin open detected 1 <sup>st</sup> discharge overcurrent detection delay time  | t <sub>DOI10</sub> |                        | 0.07                  | 0.1              | 0.13                  | S               |

| Charge overcurrent detection delay time                                            | t <sub>coı</sub>   |                        |                       | 1                |                       | s               |

| UVT pin short detected over dischargedetection delay time                          | tuvs               |                        | 2.4                   | 3                | 3.6                   | s               |

| UVT pin open detected over discharge detection delay time                          | t <sub>uvo</sub>   |                        | 0.07                  | 0.1              | 0.13                  | S               |

| OVT pin short detected over                                                        | tovs               |                        | 4.4                   | 5                | 5.6                   | S               |

| dischargedetection delay time          |                          |    |                         |            |                          |    |

|----------------------------------------|--------------------------|----|-------------------------|------------|--------------------------|----|

| OVT pin open detected over             | t <sub>ovo</sub>         |    | 0.07                    | 0.1        | 0.13                     | s  |

| discharge detection delay time         |                          |    |                         |            |                          |    |

| Temperature Protection Delay T         | ïme                      |    |                         |            |                          |    |

| Temperature detection period time      | t <sub>DETT</sub>        |    |                         | 2          |                          | S  |

| Charge over temperature detection      | 4                        |    | 3.4                     | 4          | 4.6                      | S  |

| delay time                             | t <sub>COT_DELAY</sub>   |    | 5.4                     | 4          | 4.0                      | 3  |

| Charge under temperature detection     | 4                        |    | 3.4                     |            | 4.6                      | S  |

| delay time                             | t <sub>CUT_DELAY</sub>   |    | 3.4                     | 4          | 4.0                      | 0  |

| Dischargeover temperature              | 4                        |    | 3.4                     | 4          | 4.0                      |    |

| detection delay time                   | t <sub>DOT_DELAY</sub>   |    | 3.4                     | 4          | 4.6                      | S  |

| Dischargeunder temperature             | 1                        |    |                         |            | 1.0                      | 0  |

| detection delay time                   | t <sub>DUT_DELAY</sub>   | 0. | 3.4                     | 4          | 4.6                      | S  |

| Temperature protection release         |                          |    | 2.4                     |            | 4.0                      |    |

| delay time                             | t <sub>TREL_DELAY</sub>  |    | 3.4                     | 4          | 4.6                      | S  |

| Balance Function                       |                          |    |                         |            |                          |    |

|                                        |                          |    | V <sub>BAL1</sub> -0.02 |            |                          |    |

| Level-1 Bleeding threshold voltage     | V <sub>BAL1</sub>        |    | 5                       | $V_{BAL1}$ | V <sub>BAL1</sub> +0.025 | V  |

|                                        |                          |    | V <sub>BAL2</sub> -0.02 |            | .,                       | ., |

| Level-2 bleeding threshold voltage     | $V_{BAL2}$               |    | 5                       | $V_{BAL2}$ | V <sub>BAL2</sub> +0.025 | V  |

| Level-1 allowance bleeding             |                          |    |                         |            |                          |    |

| deviation voltage between high         |                          |    | 45                      | 40         | 0.5                      |    |

| voltage battery and low voltage        | $\triangle V_{B\_ALLOW}$ |    | 15                      | 40         | 65                       | mV |

| battery                                |                          |    |                         |            |                          |    |

| Bleeding current <sup>5</sup>          | I <sub>BAL</sub>         |    |                         | 50         |                          | Ω  |

| Balance period time                    | t <sub>B</sub>           |    |                         | 0.6        |                          | S  |

| Bleeding delay time <sup>5</sup>       | t <sub>BAL_DELAY</sub>   |    |                         | 100        |                          | mS |

| Odd cells bleeding time <sup>5</sup>   | t <sub>B_ODD</sub>       |    |                         | 200        |                          | mS |

| Even cells bleeding time <sup>5)</sup> | t <sub>B_EVEN</sub>      |    |                         | 200        |                          | mS |

| Cell balancing relaxation time before  | ,                        |    |                         | 15.        |                          |    |

| cell voltage measured <sup>5)</sup>    | $t_{B\_RELAX}$           |    |                         | 100        |                          | mS |

| VCN Open-Wire Detection                |                          |    |                         |            |                          |    |

| VCN open-wire detection cycle          | t <sub>OPEN</sub>        |    |                         | 2          |                          | S  |

| 3/4/5 Cells Application Configur       |                          |    |                         |            |                          |    |

| SEL/TS pin source current              |                          |    |                         | 5          |                          |    |

| OLL/13 piii source current             | I <sub>SEL</sub>         |    |                         | J          |                          | μΑ |

| 4 Cells configuration comparator            | V <sub>SEL1</sub>  |      |      | 250         |     | mV    |

|---------------------------------------------|--------------------|------|------|-------------|-----|-------|

| threshold voltage                           | - OLL I            |      |      |             |     |       |

| 5 Cells configuration comparator            | $V_{SEL2}$         |      |      | 750         |     | mV    |

| threshold voltage                           | V SEL2             |      |      | 7 30        |     | 111.0 |

| CTLx Control                                |                    |      |      |             |     |       |

| CTLD/CTLC sink current                      | I <sub>CTL</sub>   |      |      | 1           |     | μΑ    |

| CTLD/CTLCchange voltage                     | $V_{CTL}$          |      |      | $V_{DD}$ -1 |     | V     |

| CTLC/CTLD response time                     | t <sub>CTL</sub>   |      |      | 100         |     | ms    |

| Output Voltage                              |                    |      |      |             |     |       |

| CO output voltage L                         | $V_{COL}$          |      | 0    | High_Z      | 0.5 | V     |

| CO output voltage H                         | V <sub>COH</sub>   |      |      | 12(max)     | 5   | V     |

| DO output voltage L                         | $V_{DOL}$          |      | 0    | 0           | 0.5 | V     |

| DO output voltage H                         | $V_{DOH}$          | (    | )    | 12(max)     |     | V     |

| Input Current                               |                    |      |      |             |     |       |

| VC5 pin current                             | I <sub>VC4</sub>   | S    |      | (           | 2.5 | μΑ    |

| VC4~VC1 pin current                         | I <sub>VC9~1</sub> | >    | -1.0 | 0           | 1.0 | μΑ    |

| VC0 pin current                             | I <sub>VC0</sub>   |      |      |             | 2.5 | μΑ    |

| Output Current                              |                    |      |      |             |     |       |

| CO pin maximum source current <sup>5)</sup> | I <sub>COH</sub>   | . () | · _  | 1           |     | mA    |

| DO pin maximum source current <sup>5)</sup> | I <sub>DOH</sub>   |      |      | 1           |     | mA    |

| DO pin maximum sink current <sup>5)</sup>   | I <sub>DOL</sub>   |      |      | 100         |     | mA    |

| 0V battery charge function                  |                    |      |      |             |     |       |

| 0V battery charge starting threshold        | V                  |      | 0.5  |             |     | .,    |

| voltage                                     | $V_{0CHA}$         |      | 2.5  |             |     | V     |

| 0V battery charge CO pin source             |                    |      |      | •           |     |       |

| current                                     | I <sub>0CHA</sub>  |      |      | 3           |     | μА    |

# Notes:

5) Guaranteed by design.

# **PIN DESCRIPTION**

| Pin No. | Name   | Description                                                       |

|---------|--------|-------------------------------------------------------------------|

| 1       | VDD    | Input pin for positive power supply,                              |

| 1       | VDD    | Connection pin for battery5's positive voltage                    |

| 2       | VC5    | Connection pin for battery5's positive voltage                    |

| 2       | VC4    | Connection pin for battery 5's negative voltage,                  |

| 3       | VC4    | Connection pin for battery 4's positive voltage                   |

| 4       | V(C)   | Connection pin for battery 4's negative voltage,                  |

| 4       | VC3    | Connection pin for battery 3's positive voltage                   |

| 5       | V(C)   | Connection pin for battery 3's negative voltage,                  |

| 5       | VC2    | Connection pin for battery 2's positive voltage                   |

| 6       | V/C1   | Connection pin for battery 2's negative voltage,                  |

| 6       | VC1    | Connection pin for battery 1's positive voltage                   |

| 7       | VC0    | Connection pin for battery 1's negative voltage,                  |

| 0       | CND    | Connection pin for battery 1's negative voltage,                  |

| 8       | 8 GND  | Input pin for negative power supply                               |

| 9       | OVT    | Capacitor connection pin for delay for overcharge detection       |

| 10      | VINI   | Pin for voltage detection between VINI pinand GND pin             |

| 11      | UVT    | Capacitor connection pin for delay for over discharge detection   |

| 12      | DO     | Gate connection pin for discharge control MOSFET                  |

| 13      | DOL    | Capacitor connection pin for delay for charge and discharge       |

| 13      | DOIT   | overcurrent detection                                             |

|         |        | Thermal sense input                                               |

| 14      | SEL/TS | This is a dual-purposePin. Also asSelect terminal for 3/4/5 cells |

|         |        | application                                                       |

| 15      | ТВ     | Thermal bias output                                               |

| 16      | CHSE   | Pin for charger detection                                         |

| 17      | со     | Gate connection pin for charge control MOSFET                     |

| 18      | VM     | Pin for voltage detection between VM pinand GND pin               |

| 19      | CTLC   | CO pin control input from the unit above for cascaded operation;  |

| 20      | CTLD   | DO pin control input from the unit above for cascaded operation;  |

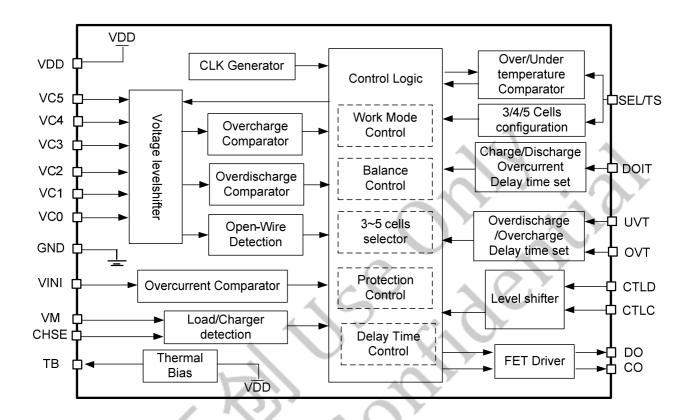

# **BLOCK DIAGRAM**

### **FUNCTIONAL DESCRIPTION**

#### **Normal Status**

In the JW3312, both of CO pin and DO pin output "H" level voltage when all battery voltages are between overdischarge detection voltage ( $V_{OD}$ ) and overcharge detection voltage ( $V_{OC}$ ), and the VINI pin's voltage is lower than 1st discharge overcurrent detection voltage ( $V_{DOI1}$ ). This is the normal status. At this time, the charge and discharge MOSFETs are on.

# **Overcharge Status**

JW3312 checks for cell over voltage once per detection time period ( $T_{DETV}$ ). When any battery voltageincreases to  $V_{OC}$  or more for longer than the overcharge detection delay time ( $t_{OC}$ ), the CO pin outputs "High\_Z". Since the CO pin pulled down to the CHA- voltage by an external resistor, the charge MOSFET is turned off to stop charging. This is the overcharge status.

The overcharge status is released if one of the conditions mentioned below is satisfied:

- (1) All batteryvoltagedrops to overcharge release voltage (V<sub>OCL</sub>) or less.

- (2) The VINI pin voltage is higher than  $V_{TH\_DSG}$  during discharging and all batteryvoltagedrops to overcharge voltage  $(V_{OC})$  or less.

### **Overdischarge Status**

JW3312 checks for cell under voltage once per detection time period ( $T_{DETV}$ ). When any voltage of the batteries decreases to the level of  $V_{OD}$  or less for longer than the overdischarge detection delay time ( $t_{OD}$ ), the DO pin outputs "L" voltage. The discharge MOSFET is turned off and it stops discharging. This is the overdischarge status.

The VM pin is pulled down to the GND level via

R<sub>VMS</sub> internally.

The overdischarge status is released if either condition mentioned below is satisfied:

- (1) The VM pin voltage is 1V or less, and all battery voltages increase to overdischarge release voltage (V<sub>ODH</sub>) or more.

- (2) Any battery voltage gets to be higher than  $V_{OC}$  or more for longer than  $t_{OC}$ .

# **Discharge Overcurrent Status**

In the JW3312, if the VINI pin voltage increases to the level of  $V_{\text{DOI}}$  or morefor longer than the discharge overcurrent detection delay time ( $t_{\text{DOI}}$ ), the DO pin outputs "L" voltage. The discharge MOSFET is turned off and it stops discharging. This is the discharge overcurrent status.

The VM pin is pulled down to the GND level via  $R_{\text{VMS}}$  internally.

JW3312 has three levels for discharge overcurrent detection ( $V_{DOI1}$ ,  $V_{DOI2}$ ,  $V_{SHT}$ ). The JW3312 actions against load short circuit detection voltage ( $V_{SHT}$ ) are as well in  $V_{DOI}$ .

The discharge overcurrent status is released if the following condition is satisfied.

(1) The VM pin voltage gets 1V or less.

### **Charge Overcurrent Status**

In the JW3312, if the VINI pin voltage decreases to the level of  $V_{\text{COI}}$  or lower for longer than the charge overcurrent detection delay time ( $t_{\text{COI}}$ ), the CO pin outputs "Hi-z". The charge MOSFET is turned off and it stops charging. This is the charge overcurrent status.

The CHSE pin is pulled up to the 5V regulatorvia resistor internally.

Charge overcurrent protection will be released when we disconnect the charger.

# **Delay Time Setting**

In the discharge over current and over discharge detection, users are able to set the delay time by a current in JW3312 and an external capacitor.

Take the discharge overcurrentdetectionfor example, when the VINI pin voltage gets  $V_{DOI1}$  or more, JW3312 starts charging to the DOIT pin's capacitor ( $C_{DOIT}$ ) via the DOIT pin's output current ( $I_{DOIT}$ ). After a certain period, the DO pin outputs "L" voltage. This period is the 1st dischageovercurrent detection delay time ( $t_{DOI1}$ ), which is calculated using the following equation.

$t_{DOI1}[s] = n \times \Delta V \times C_{DOIT}[nF] / I_{DOIT}[uA]$

=

$$400(typ.) \times C_{DOIT}[nF] / 8[uA] (typ.)$$

=

$$50[M\Omega](typ.) \times C_{DOIT}[nF]$$

In case C<sub>DOIT</sub>=2nF, t<sub>DOI1</sub> is calculated as follows.

$$t_{DOI1}[s] = 50[M\Omega](typ.) \times 2[nF] = 0.1[s](typ.)$$

The  $2^{nd}$  discharge overcurrent detection delay time ( $t_{DOI2}$ ) is calculated as below.

$$t_{DOI2}=t_{DOI1}\times0.1$$

The function of overdischarge detection delay time is same to the discharge overcurrent detection delay time.

The function of overcharge detection delay time is same to the discharge overcurrent detection delay time.

The loadshort circuit detection delay time are fixed internally.

# **Fault Detection on DOIT& UVT**

To set the dischargeovercurrent detection delay time and theoverdischarge detection delay time,

a capacitor is connected between DOIT/UVT pin and GND pin.

Take the discharge overcurrent for example. If the discharge overcurrent is detected and the DOIT pin is shorted to ground,  $t_{DOI1}$  is automatically changed to the DOIT pin short detected  $1^{st}$  discharge overcurrent detection delay time ( $t_{DOI1S}$ ).

In the same manner, if the discharge overcurrent is detected and the DOIT pin is floating,  $t_{DOI1}$  is automatically changed to the DOIT pin open detected  $1^{st}$  discharge overcurrent detection delay time ( $t_{DOI10}$ ).

The fault detection function of pin UVT is similar to the pin DOIT.

# **Temperature Protection**

When the VINI pin voltage is bigger than  $V_{TH\_DSG}$ , the battery pack is regarded as in discharging status. Otherwise, the battery pack is regarded as in charging status.

The JW3312do the temperature detection every  $t_{\text{DETT}}$ , see figure 1 for temperature detection timing chart. In normal status, the JW3312 continuously turns on TB output for  $t_{\text{EFF\_DETT}}$  every  $t_{\text{DETT}}$ . When the TB output turns on, the external temperature is monitored.

Figure 1 temperature detection timing

When the temperature of battery pack increases, the voltage of the TS pin decreases. Once the battery temperature is over the Charging/Discharging OverTemperature Threshold and the state continues for  $t_{\text{COT\_DELAY}}$ , JW3312 shuts down both the charge and discharge MOSFETs. This status is released only when the battery temperature goes down.

When the battery pack temperature becomes lower than  $T_{\text{CUT}}$  in charging status and the state continues for  $t_{\text{CUT\_DELAY}}$ , the charging and discharging FETs is turned off to stop charging and discharging. The charging under-temperature status is released only when the battery pack temperature becomes higher.

When the battery pack temperature becomes lower than  $T_{DUT}$  in discharging status and the state continues for  $t_{DUT\_DELAY}$ , the charging and discharging FETs is turned off to stop charging and discharging. The discharging under-temperature status is released only when the battery pack temperature becomes higher.

he CTLC/CTLD pin is used for cascaded operation. When any error is detected such as over-charge, over-discharge, open-wire in the upper unit, the CO/DO pin signal are passed down to the CTLC/CTLD pinof the lower unit to control charging/discharging.

When the CTLC/CTLD pin of the top cell isdirectly connected to VDD pin, JW3312 works normally. If the CTLC/CTLD pin of the top cell is connected to VDD pin via external 2M resistor, the CO/DO pin voltage is forced to be "L". As a result, JW3312 enters the charge/discharge disable mode and the charge/discharge MOSFET is forced off.

External FET's state by CTLx pins

| CTLC pin      | External FET for CO pin |

|---------------|-------------------------|

| GND           | High Z                  |

| No connection | High Z                  |

| VDD           | ON (normal operation)   |

| CTLD pin      | External FET for DO pin |

|---------------|-------------------------|

| GND           | Forced OFF              |

| No connection | Forced OFF              |

| VDD           | ON (normal operation)   |

### **Operation Modes**

JW3312 has twooperation modes: Full power mode, and Sleep mode.

For Full power mode, JW3312 checks for over-voltage, overdischarge-voltage events and over-temperature every detection period. Besides, over-current events are checked continuously. These safety events decide the status of the charge and discharge MOSFETs. The typical current consumption is 15uA.

JW3312 enters Sleep mode after entering over-discharge status, over-temperature status, under-temperature status or open wire status. The typical current consumption is lower down to be 2uA at sleep mode.

For the other case, JW3312 only waits for temperature events or open wire events releasing.

JW3312 enters Shutdown mode when VDD pin voltage becomes lower than  $V_{\text{PDOWN}}$ . During this mode, JW3312 does not check for any safety events. The charge and discharge MOSFET are both off. The typical current consumption is as low as 350nA.

#### **Balance Function**

JW3312 provides cells' balance function to balance the cells' capacity in a battery pack. When any cell voltage is higher than Level-1 bleeding threshold voltageV<sub>BAL1</sub>, and the cell voltage is higher than the lowest cell  $\triangle$  V<sub>B\_ALLOW</sub>, theoff-chip balance will be turn on and provide about 100mA bleeding current.

Odd-even balance strategy is adopted. The balance period time is 600mS. The first 100mS is used for over/under voltage detection. The second 200mS is used for the odd cells bleeding that satisfy the balance conditions. The

third 200mS is used for the even cellsbleeding that satisfy the balance conditions. The last 100mS is cell balancing relaxation time before cell voltage measured

When the JW3312 is used in extended condition, to avoid the unbalance between IC1 and IC2, the JW3312 provide level-2 balance function.If all the five cell voltage exceed the Level-2 bleeding threshold voltage  $V_{BAL2}$ , the external discharge MOS turn on.

The balance exitsif one of the conditions mentioned below is satisfied:

(1) When all voltages of VC1, (VC2-VC1), (VC3-VC2), (VC4-VC3) and (VC5-VC4) are lower  $V_{BAL1}$ , or higher than VBAL1 and

- Lower than  $V_{BAL2}$ , all the external balance discharge circuits will not work.

- (2) When any battery voltage is higher than  $V_{BAL1}$ , but lower than the lowest  $\triangle V_{B\ ALLOW}$

- (3) The system entries sleep mode

# **Open-wire Detection**

JW3312 checks for VC5-VC0open-wire once per detection time period  $t_{\text{OPEN}}$ .

When any of V5 to V0 pin open, it will detect open-wire and charge and discharge is prohibited

The release from open-wire protection is done by open-wire point being connected and VDD power on again.

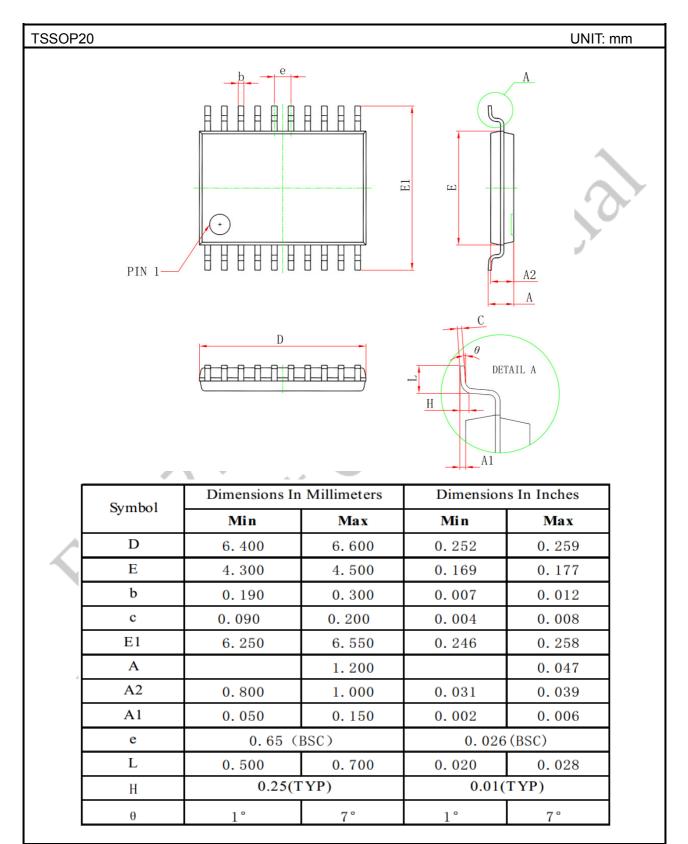

# **PACKAGE OUTLINE**

# **IMPORTANT NOTICE**

Joulwatt Technology Inc. reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Inc. does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

All rights are reserved by Joulwatt Technology Inc.