# ANGUS ELECTRONICS COMPANY LIMITED

Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

T100A Advanced Information-Confidential P/N-T100A-Rev02

Advanced Information Version 0.3

June, 06, 2005

# **T100A Video Display Controller**

|          |               | Contents                                       |               |

|----------|---------------|------------------------------------------------|---------------|

|          | Section       | Title                                          | Page          |

| <u>1</u> |               | uction                                         | 3             |

| <u> </u> | 1.1           | Features                                       | 3             |

|          | 1.2           | General Description                            | 4             |

|          | 1.3           | Applications                                   | 4             |

|          | 1.4           | System Architecture                            | 4             |

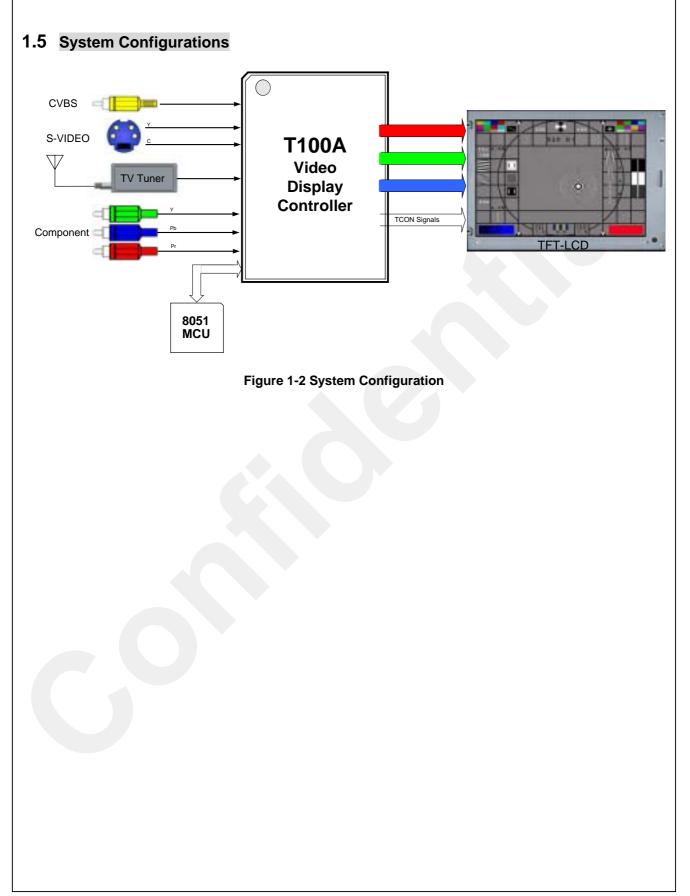

|          | 1.5           | System Configurations                          | 5             |

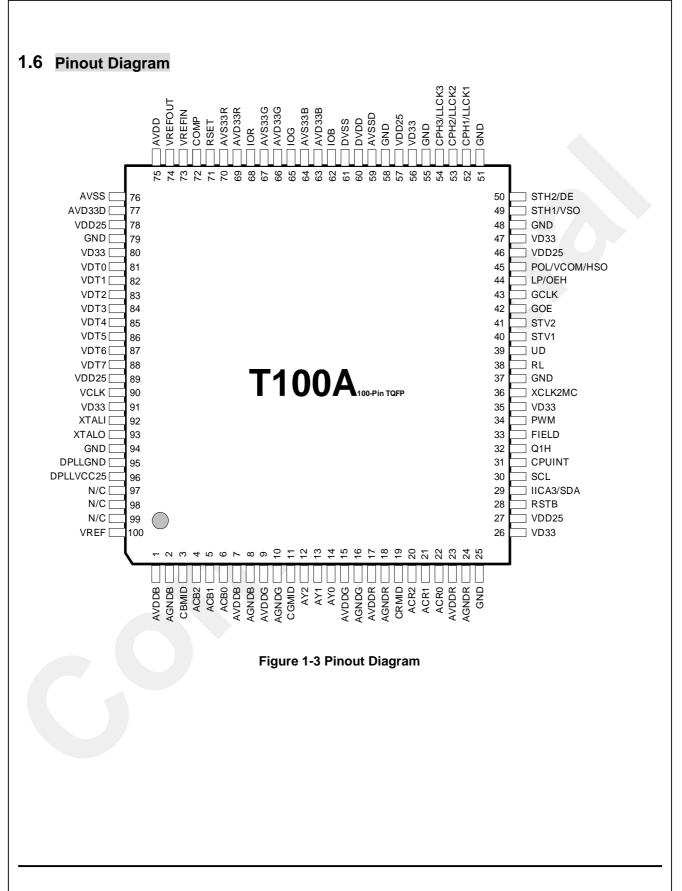

|          | 1.6           | Pinout Diagram                                 | 6             |

| _        | 1.7           | Pin Description                                | 7             |

| <u>2</u> | <u>Theor</u>  | y of Operations                                | <b>9</b><br>9 |

|          | 2.1           | I <sup>2</sup> C Command Protocol              |               |

|          | 2.2           | Analog Front End                               | 11            |

|          | 2.3           | Y/C Separation and Chroma Decoder              | 11            |

|          | 2.4           | Digital Color Transient Improvement (DCTI)     | 13            |

|          | 2.5           | Digital Luminance Transient Improvement (DLTI) | 14            |

|          | 2.6           | FIR Scaler                                     | 14            |

|          | 2.7           | Black-Level Extension (BLE)                    | 15            |

|          | 2.8           | Color Space Converter                          | 15<br>16      |

|          | 2.9<br>2.10   | Gamma Correction OSD                           | 10            |

|          | 2.10          | TCON                                           | 29            |

| 2        |               | ter Description                                |               |

| <u>3</u> | 3.1           | ADC Register Set                               | <b>32</b>     |

|          | 3.1           | Picture Enhancement Register Set               | 44            |

|          | 3.3           | Scaling Register Set                           | 46            |

|          | 3.4           | Color Space Converter Register Set             | 40<br>52      |

|          | 3.5           | OSD Register Set                               | 55            |

|          | 3.6           | LCD Output Control Register Set                | 56            |

|          | 3.7           | TCON Register Set                              | 66            |

|          | 3.8           | ITU - 656 Decoder Register Set                 | 71            |

|          | 3.9           | Y/C Separation and Chroma Decoder Register Set | 74            |

| 4        | Electr        | ical Characteristics                           | 80            |

| -        | 4.1           | Digital I/O Pad Operation Condition            | 80            |

|          | 4.2           | DC Characteristics                             | 81            |

|          | 4.3           | AC Characteristics                             | 82            |

|          | 4.4           | Analog Processing and A/D Converters           | 82            |

|          | 4.5           | Absolute Maximum Rating                        | 82            |

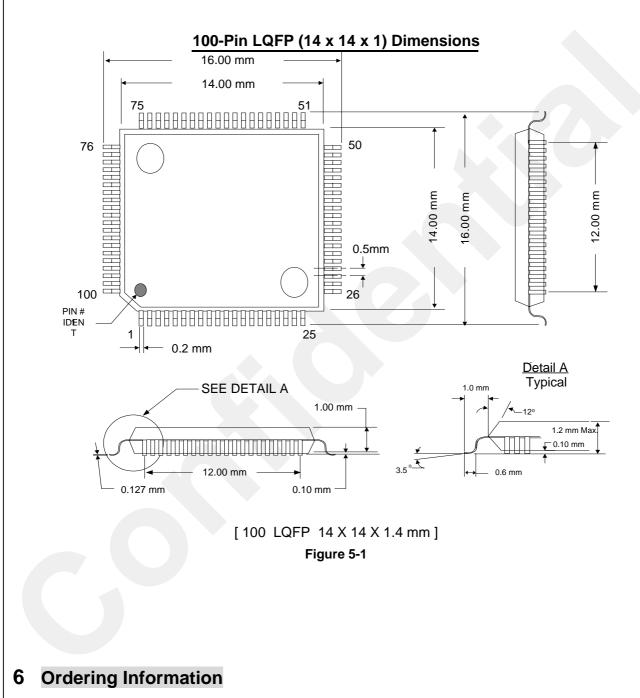

| <u>5</u> | Packa         | ge Dimensions                                  | 83            |

|          |               |                                                |               |

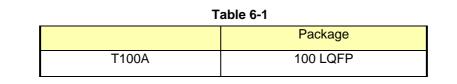

| <u>6</u> | <u>Orderi</u> | ing Information                                | 83            |

| <u>7</u> | Revisi        | ions Note                                      | 84            |

| <u>8</u> | Gener         | al Disclaimer                                  | 84            |

|          |               |                                                |               |

| <u>9</u> | <u>Conta</u>  | ct Information                                 | 84            |

#### . .

### **1** Introduction

### 1.1 Features

- Cost Effective Highly Integrated Triple ADC + + 2D Video Decoder + OSD + VBI Data Decoder+ Scaler + TCON

- Integrates 9-bit Triple Analog to Digital Converters (ADC) & Phase Locked Loop (PLL)

- Scaler supports 2-D adaptive intra-field deinterlacer and non-linear 16:9 aspect ration.

- Requires no external Frame Buffer Memory for deinterlacer.

- Advanced On Screen Display (OSD) function

- Programmable Timing Controller (Tcon) for Car TV applications

- Multi-standard color decoder with 2D adaptive comb filter

- Innovative and flexible design to reduce total system cost

### Triple 9-bit Analog to Digital Converters (ADC)

#### 80MSPS Conversion Rate

- Built-in Pre-amp, mid-level & ground clamp circuit

- Automatic Clamp Control for CVBS, Y and C

- Programmable Static Gain Control or Automatic Gain Control for CVBS or Y/C

- Max Input configuration up to 9xCVBS, 3xSvideo and 3xCVBS, 3xYPbPr,

#### Digital Video Enhancement

#### Separate Luminance and Chroma Enhancer

- Y Supports Luminance Peaking, DLTI, Black Level Expansion, Contrast and Brightness adjustment

- C Supports DCTI, Saturation and Hue adjustment.

#### Advanced Scaling Engine

#### Two Dimensions FIR Scaler

- Coefficient based sharpness filters

- 2-D edge enhancement

- Independent vertical and horizontal scaling ratio

- 16:9 Non-linear Aspect ratio

- LCD Interface

- Provides Gamma correction for panel compensation

- Supports image pan functions

- Programmable Timing Controller

- RGB Triple DAC output

#### Color Management

- Coef Programmable YCbCr-to-RGB Color Space Converter

- RGB Gamma Correction

# Built-in On Screen Display Engine 3K-word OSD SRAM memory

- 3K-word OSD SRAM memory

- Supports font or bitmap modes

- Supports character blinking, overlay, shadow and border functions

- Fully programmable character mapping

- Supports alpha blending & Zoom-in/Zoomout function

- Optional fonts can be stored in off-chip serial EEPROM

#### Versatile VBI Data Decoder

Supports Close Caption, Wide Screen Signalling and Teletext

#### Crystal Oscillator Circuit

- Direct interface to a (27.0MHz) Crystal

- Also provide a buffered clock output for external Micro-controller

#### Digital Test Pattern Generator

- Programmable standard & special panel burn-in test patterns

- Support special border frame blocking mode

#### Independent Display Phase Lock Loop

- Generates pixel clock output to panel

- Supports free run OSD mode

- Serial Bus Interface

- Supports 2-wire (normal speed) or 4-wire (high speed) modes

- Pulse Width Modulation Outputs

- Design For Testability

- Scan chain insertion

- Separated analog & digital test modes

- Power Supply: +2.5V & +3.3V

- Package: 100-pin LQFP

### 1.2 General Description

The T100A is a highly integrated All-in-one Visual Processor that provides major cost saving solution for the portable applications. T100A has built-in high performance Triple ADCs, TCON, Triple DACs, Scaling Machine with sophisticated upscaling and downscaling algorithms. The Innovative integrated "Frame-Buffer-Less" De-interlacer can significantly reduce system cost. The T100A also integrates On Screen Display engine with 3K-word of font RAM. The device can interface to an external micro-controller through 2-wire serial bus interface.

### 1.3 Applications

- 1. 4-inch to 10-inch portable DVD or in-car TV

- 2. Progressive CRT TV

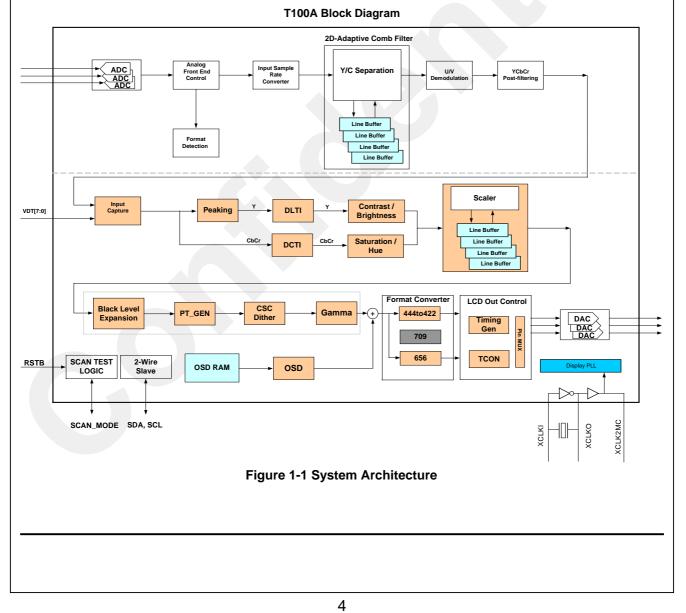

### **1.4 System Architecture**

# 1.7 Pin Description

| Symbol      | Pin #                               | Туре    | Description                                       |

|-------------|-------------------------------------|---------|---------------------------------------------------|

| Power Supp  | lies                                |         |                                                   |

| VDD25       | 27,46,57,78,<br>89,96               | PWR     | +2.5V digital core power supply                   |

| VD33        | 26,35,47,56,<br>80,91               | PWR     | +3.3V digital output power supply                 |

| AVDDB       | 1, 7                                | PWR     | +3.3V analog power supply for ADC channel 2       |

| AVDDG       | 9, 15                               | PWR     | +3.3V analog power supply for ADC channel 1       |

| AVDDR       | 17, 23                              | PWR     | +3.3V analog power supply for ADC channel 0       |

| GND         | 25, 37,48,<br>51,55,58,79,<br>94,95 | GND     | Digital ground                                    |

| AGNDB       | 2, 8                                | GND     | Analog ground for ADC channel 2                   |

| AGNDG       | 10, 16                              | GND     | Analog ground for ADC channel 1                   |

| AGNDR       | 18, 24                              | GND     | Analog ground for ADC channel 0                   |

| AVD33R      | 69                                  | PWR     | +3.3V analog power supply for DAC channel R       |

| AVD33G      | 66                                  | PWR     | +3.3V analog power supply for DAC channel G       |

| AVD33B      | 63                                  | PWR     | +3.3V analog power supply for DAC channel B       |

| AVDD        | 75                                  | PWR     | +2.5V Analog Power Supply for DAC                 |

| DVDD        | 60                                  | PWR     | +2.5V Digital Power Supply for DAC                |

| AVD33D      | 77                                  | PWR     | +3.3V Analog Power Supply for DAC I/O pads        |

| AVSS3R      | 70                                  | GND     | Analog ground for DAC channel R                   |

| AVSS3G      | 67                                  | GND     | Analog ground for DAC channel G                   |

| AVSS3B      | 64                                  | GND     | Analog ground for DAC channel B                   |

| AVSS        | 76                                  | GND     | Analog ground for DAC                             |

| DVSS        | 61                                  | GND     | Digital ground fro DAC                            |

| AVSSD       | 59                                  | GND     | Analog Ground for DAC I/O pads                    |

| Output Inte | rface Signals                       | ;       |                                                   |

| IOR         | 68                                  | AO      | Channel R current output                          |

| IOG         | 65                                  | AO      | Channel G current output                          |

| IOB         | 62                                  | AO      | Channel B current output                          |

| LLCK1       | 52                                  | DO      | Output Data Clock                                 |

| LLCK2       | 53                                  | DO      | Output Data Clock                                 |

| LLCK3       | 54                                  | DO      | Output Data Clock                                 |

| VSO         | 49                                  | DO      | Vertical Synchronization Output Control Signal.   |

| HSO         | 45                                  | DO      | Horizontal Synchronization Output Control Signal. |

| Timing Cont | roller Interfa                      | ce Sigr | nals                                              |

| STH2        | 50                                  | DO      | Source Driver start pulse                         |

| LP          | 44                                  | DO      | Latch pulse for column driver                     |

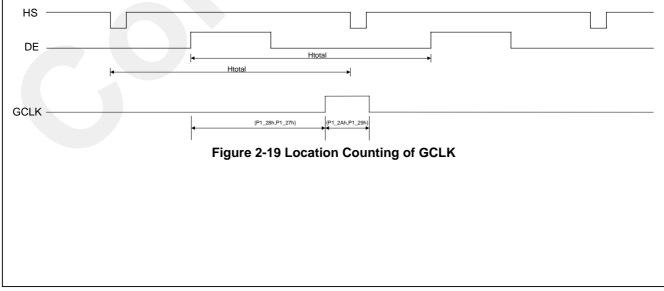

| GCLK        | 43                                  | DO      | Gate driver clock                                 |

| GOE         | 42                                  | DO      | Gate driver output enable                         |

| STV1        | 40                                  | DO      | Gate Driver start pulse                           |

| STV2        | 41                                  | DO      | Gate Driver start pulse                           |

| UD          | 39                                  | DO      | Panel UP/Down Control                             |

| RL          | 38                                  | DO      | Panel Right/Left Control                          |

| Q1H         | 32                                  | DO      | Source Driver Q1H                                 |

#### Table 1-1 Pin Description

| Symbol        | Pin #       | Туре    | Description                                              |

|---------------|-------------|---------|----------------------------------------------------------|

| 2-wire serial | bus Interfa | ce Sign | als                                                      |

| SCL           | 30          | DI      | 2-wire serial bus clock. Power down does not affect SCL. |

| SDA           | 29          | I/O     | 2-wire serial bus data. Power down does not affect SDA.  |

| Configuratio  | n interface | Signals |                                                          |

| CPUINT        | 31          | I/O     | Internal Interrupt.                                      |

| RSTB          | 28          | DI      | Whole chip reset. (Internal Pull-up)                     |

| Test Pins     |             |         |                                                          |

| FIB1          | 99          | AO      | ADC test pin                                             |

| FILED         | 33          | DO      | Field flag                                               |

| ADC Interfac  | е           |         |                                                          |

| ACB2          | 4           | AI      | Analog input 2 of channel 2                              |

| ACB1          | 5           | AI      | Analog input 1 of channel 2                              |

| ACB0          | 6           | AI      | Analog input 0 of channel 2                              |

| AY2           | 12          | AI      | Analog input 2 of channel 1                              |

| AY1           | 13          | AI      | Analog input 1 of channel 1                              |

| AY0           | 14          | AI      | Analog input 0 of channel 1                              |

| ACR2          | 20          | AI      | Analog input 2 of channel 0                              |

| ACR1          | 21          | AI      | Analog input 1 of channel 0                              |

| ACR0          | 22          | AI      | Analog input 0 of channel 0                              |

| Video-In Inte | rface       |         |                                                          |

| VCLK          | 90          | DI/O    | ITU-656 video clock                                      |

| VDT0          | 81          | DI/O    | ITU-656 video port                                       |

| VDT1          | 82          | DI/O    | ITU-656 video port                                       |

| VDT2          | 83          | DI/O    | ITU-656 video port                                       |

| VDT3          | 84          | DI/O    | ITU-656 video port                                       |

| VDT4          | 85          | DI/O    | ITU-656 video port                                       |

| VDT5          | 86          | DI/O    | ITU-656 video port                                       |

| VDT6          | 87          | DI/O    | ITU-656 video port                                       |

| VDT7          | 88          | DI/O    | ITU-656 video port                                       |

| PLL Referen   | ce Clock    |         |                                                          |

| XTALI         | 92          | DI      | Output PLL reference clock input                         |

| XTALO         | 93          | DO      | Output PLL reference clock output                        |

| XCLK2MC       | 36          | DO      | Buffered XTALI for external microprocessor.              |

| Power Manag   | gement Inte | rface S | ignals                                                   |

| PWM           | 34          | DO      | Pulse Width Modulation for backlight control.            |

### 2 Theory of Operations

### 2.1 I<sup>2</sup>C Command Protocol

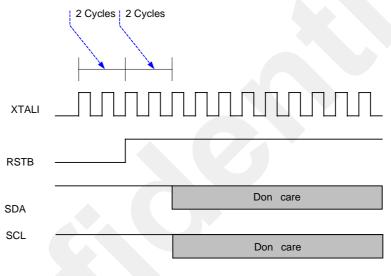

Before your tester writes I<sup>2</sup>C commands to T100A, slave address must be set at 50h. The timing sequence can be shown as below. After 4 cycles, the tester can get started IIC commands. SDA(A3) can affect slave address. Set low for 40h. Set high for 50h.

Figure 2-1 Power-up initialization

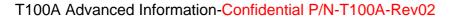

When tester issues commands to the T100A, the only way the user can program the T100A is using the 2-wire serial bus protocol. This section describes the 2-wire serial bus protocol. Data transfers on the 2-wire serial bus are initiated with a START condition and are terminated with a STOP condition. Normal data on the SDA line must be stable during the high period of the SCL. The transition on the SDA is only allowed while SCL is low. The START condition is unique case and is defined by a high-to-low transition on the SDA while the SCL is high. The STOP condition is a unique case and is defined by a low-to-high transition on the SDA while the SCL is high. Each data packet on the 2-wire serial bus consists of 8 bits of data followed by an ACK bit. Data is transferred with MSB first. The transmitter releases the SDA line during the ACK bit and the receiver of data transfer must drive the SDA line low during the ACK bit to acknowledge receipt of the data. The frequency of SCL can be from 50 Khz up to 1 Mhz.

### 2.2 Analog Front End

Figure 1-1

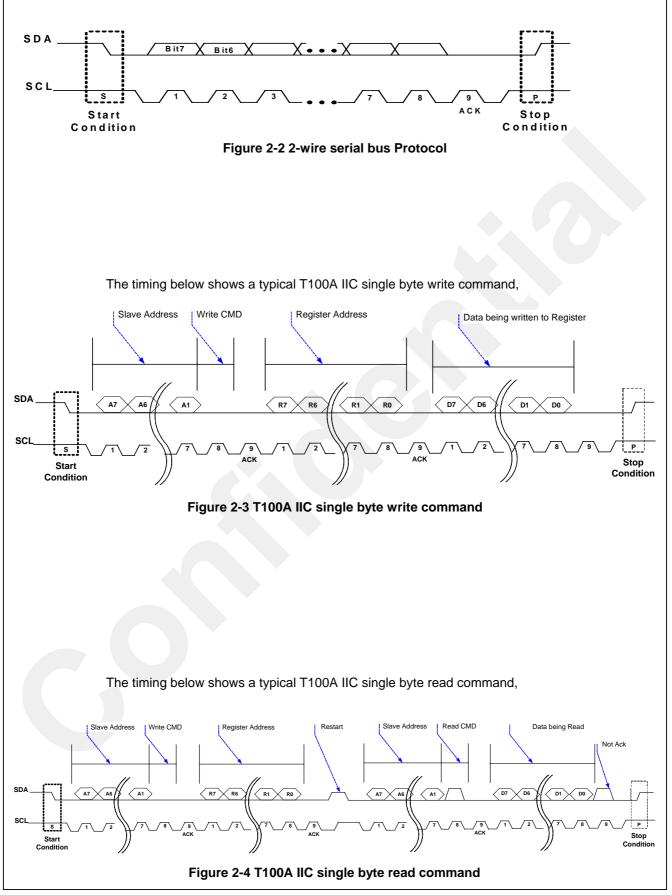

T101 contains 3 ADCs in Analog Front End. Each channel of ADCs can digitalize SDTV signals from analog to digital. The figure shown below can describe how to select a SDTV signal from 3 inputs prior to ADC.

Figure 2-5 Analog Front End

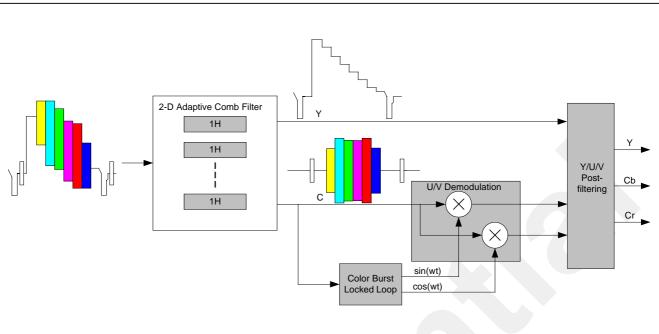

### 2.3 Y/C Separation and Chroma Decoder

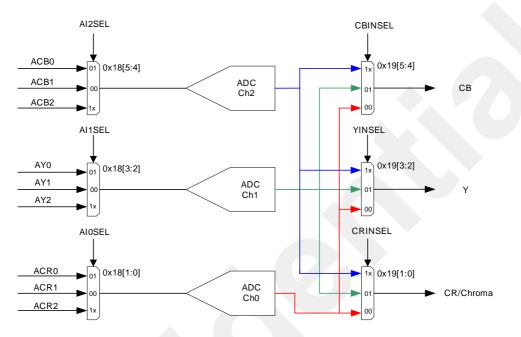

A composite video has luma(Y) and chroma(C) information mixed in the same video signal. This video signal can also be represented by the equation below,

$$CVBS = Y + U * Sin(wt) + V * cos(wt)$$

Where  $w = 2\pi f_{sc}$ ,  $f_{sc}$  =3.58Mhz if NTSC,  $f_{sc}$  =4.43Mhz if PAL

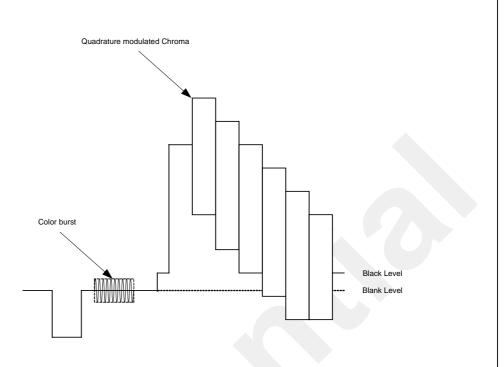

The figure below shows a typical composite signal. The 2-D adaptive comb filter inside T100A is designed to separate Y and C from a composite video signal.

#### Figure 2-6

. The conventional 3-line comb filter fails to separate Y and C if there is a vertical transition. The 2-D adaptive comb filter is based on equally weighting factors that color changes along vertical and horizontal edges. Let the amount of color change along vertical and horizontal direction DCv and DCh, the weighting factor can be expressed as following equations,

$$Wh = \frac{DCv}{DCv + DCh}$$

$$Wv = \frac{DCh}{DCv + DCh}$$

By employing adaptive method, chroma can be recovered by following equation, C = Ch \* Wh + Cv \* Wv

After Y/C separation, Y and C should look like waveforms shown as in following figure. Y only contains low frequency part, while C contains high frequency part which is centered around subcarrier  $f_{sc}$ .

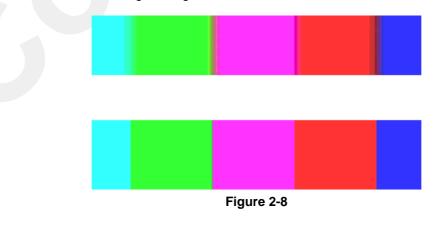

### 2.4 Digital Color Transient Improvement (DCTI)

Usually, a composite or S-video SDTV signal may have bandwidth limitation that causes the loss chroma detail around two different color bars. Two pictures shown below illustrate the result before and after DCTI block. Without DCTI(the upper picture), we may see color transient wider than several pixels. A slow transient edge usually blurs image. T100A DCTI algorithm can sharpen those color transient edges. The lower picture shows that chroma data is enhanced by increasing the slope of edge transient without introducing the ring effects.

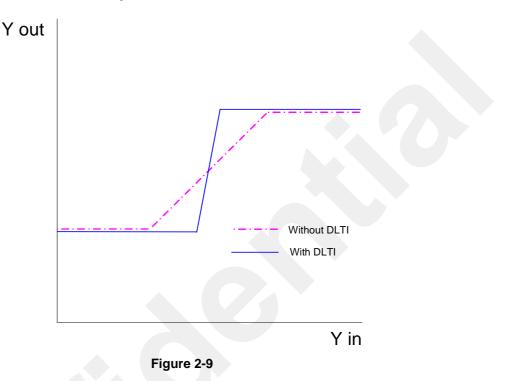

### 2.5 Digital Luminance Transient Improvement (DLTI)

The Digital Luminance Transient Improvement is intended to sharpen luminance edge transient. The figure shown below is DLTI transfer function. DLTI doesn't increase peak-to-peak amplitude; rather it turns sloped waveforms into rectangular waveforms.

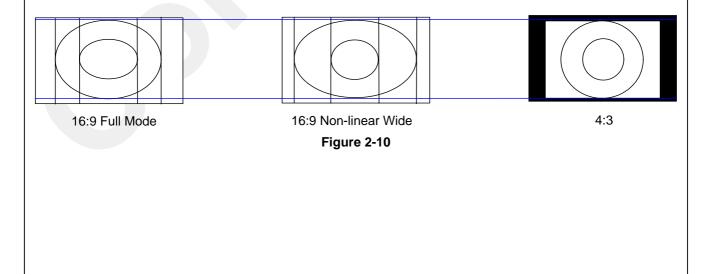

### 2.6 FIR Scaler

FIR Scaler can scale input H/V sizes to fit any LCD panel resolution. The flexible and independent H/V scalers allow users to program display area in 16:9 Full mode, 16:9 non-linear wide mode and 4:3 mode. FIR scaler also provides coefficient-based 2-D sharpness that can sharpen detail of picture.

### 2.7 Black-Level Extension (BLE)

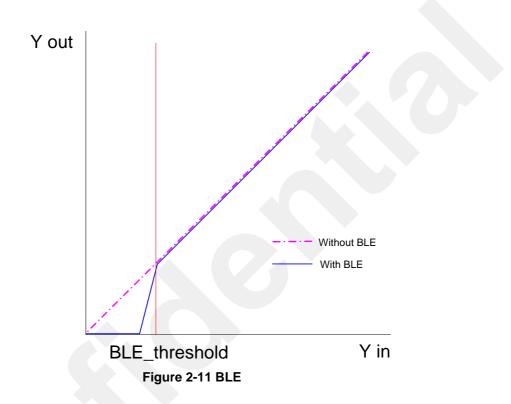

Black Level Expansion (BLE) can enhance image contrast that makes dark regions of image darker, while bright regions remain unchanged. The figure shown below is BLE transfer function.

$Yout = Yin - (Yoffset - Yin) * BLE \_Gain / 16$ Where *Yoffset* and *BLE \_Gain* can be programmed by register P0\_96h.

### 2.8 Color Space Converter

A pixel in YCbCr color space can be converted to RGB color space by using following equations,

$$R = YCoefCSC * (Y - 16) + CrCoef \_ R * (Cr - 128)$$

$$G = YCoefCSC * (Y - 16) - CrCoef \_ G * (Cr - 128) - CbCoef \_ G * (Cb - 128)$$

$$B = YCoefCSC * (Y - 16) + CbCoef \_ B * (Cb - 128)$$

Where YCoefCSC is in 1.7-bit fixed point with default 1.164.  $CrCoef \_R$  in 1.7-bit fixed point with default 1.596.  $CrCoef \_G$  in 0.8-bit fixed point with default 0.813.  $CbCoef \_G$  in 0.8-bit fixed point with default 0.392.  $CbCoef \_B$  in 2.6-bit fixed point with default 2.017

The equations shown as below correspond to a typical YCbCR-to-RGB converter. In T101, we make those coefficients adjustable.

$$R = 1.164 * (Y - 16) + 1.596 * (Cr - 128)$$

$$G = 1.164 * (Y - 16) - 0.813 * (Cr - 128) - 0.392 * (Cb - 128)$$

$$B = 1.164 * (Y - 16) + 2.017 * (Cb - 128)$$

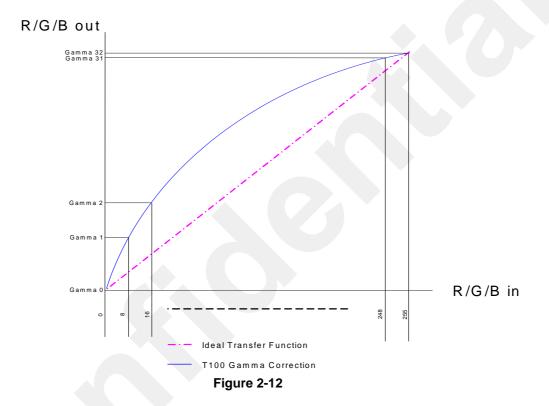

### 2.9 Gamma Correction

The relation between input video signal and LCD panel may exist non-linear transfer function such as figure shown below,

T100A uses 33-point piece-wise linear interpolation instead of RAM-based LUTs. Each point can be programmed via register at P0\_93h and P0\_94h.

### 2.10 OSD

### 2.10.1 OSD Access

| I/O Port        | Index | Default | Description                                                                                            |

|-----------------|-------|---------|--------------------------------------------------------------------------------------------------------|

|                 | 00h   | 00h     | OSD Control Register                                                                                   |

|                 | 01h   | 00h     | Character Delay_1                                                                                      |

|                 | 02h   | 10h     | Character Delay_2                                                                                      |

|                 | 03h   | 08h     | Character Delay_3                                                                                      |

|                 | 04h   | 09h     | Character Font Size                                                                                    |

|                 | 05h   | 50h     | Char_RAM Base Address                                                                                  |

|                 | 06h   | 00h     | Character Border / Shadow Control                                                                      |

|                 | 07h   | 00h     | Character Border / Shadow Color                                                                        |

|                 | 08h   | 20h     | Character Height Scaling                                                                               |

|                 | 09h   | 0Ah     | Blinking Control                                                                                       |

|                 | 0Ah   | 00h     | Bit_Map Window Size : Width/Height Upper Bits                                                          |

|                 | 0Bh   | 80h     | Bit_Map Window Size : Width                                                                            |

| A0h – Cfg_Index | 0Ch   | 60h     | Bit_Map Window Size : Height                                                                           |

| 0-              | 0Dh   | 11h     | Bit_Map Dot Enlarge                                                                                    |

| A1h – Cfg_Data  | 0Eh   | -       | OSD LUT RAM Data R/W, address automatically increased after R or W                                     |

|                 | 0Fh   | 00h     | Char RAM Byte Access Control                                                                           |

|                 | 10h   | 00h     | Window_1 Start Character Row Number / BMP Start Address LSB                                            |

|                 | 11h   | 00h     | Window_1 End Character Row Number / BMP Start Address MSB                                              |

|                 | 12h   | 00h     | Window_1 Start Character Column Number                                                                 |

|                 | 13h   | 00h     | Window_1 End Character Column Number                                                                   |

|                 | 14h   | 00h     | Window_1 Shadow Size                                                                                   |

|                 | 1Ah   | 00h     | Char2BP Base Address LSB                                                                               |

|                 | 1Bh   | 08h     | Char2BP Base Address MSB                                                                               |

|                 | 1Ch   | 00h     | Alpha Blending Control (available Revision >=02h)                                                      |

|                 | 1Dh   | 03h     | Revision ID                                                                                            |

|                 | 1Eh   | 60h     | Char_RAM Stop Address (available Revision >=01h)                                                       |

|                 | Other | 00h     | Reserved                                                                                               |

| A2h – ORAM_AL   |       | 00h     | OSD RAM Low Address Port of Starting Access                                                            |

| A3h – ORAM_AH   |       | 00h     | OSD RAM High Address Port of Starting Access                                                           |

| A4h – ORAM_D    |       | 00h     | OSD RAM Data Port (Low Byte first, then High Byte). After two R/W, the address will be increased by 1. |

Table 2-1

### 2.10.3 Character RAM Format

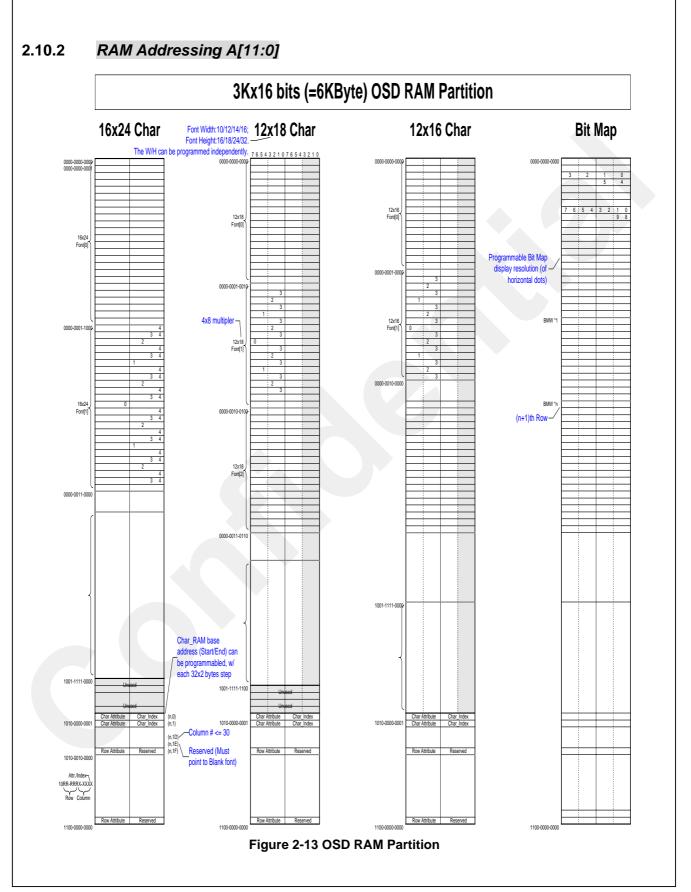

In Character Mode (contrast to Bit\_Map Mode), the Characters displayed on OSD can be grouped to few rows, each row has its own row attribute (the high byte of Word  $\#1F_h$ , ref. Section 2.10.3.3) which defines the behavior of current character row. And, there is maximum 30 characters in one row (Word  $\#00_h \sim \#1D_h$ ), each character has two bytes to define its character font number (ref. Section 2.10.3.1) and its colors (ref. Section 2.10.3.2). And the Word  $\#1E_h$  is reserved, which must be filled with transparent color and pointed to blank font.

### 2.10.3.1 Character Data (Address to Font Select) (Default=XXXXXXXb<sup>1</sup>)

| <br>7   | 6                                              | 5       | 4                                                | 3                   | 2                                          | 1       | 0       |

|---------|------------------------------------------------|---------|--------------------------------------------------|---------------------|--------------------------------------------|---------|---------|

| CHRA[7] | CHRA[6]                                        | CHRA[5] | CHRA[4]                                          | CHRA[3]             | CHRA[2]                                    | CHRA[1] | CHRA[0] |

| Bit 7-0 | number N, the<br>Cfg_04h<4:3><br>Index 00h~BFI |         | font, and that for<br>.4.5).<br>(mono colored) f | nt starting address | (i.e., 0,1,2, A,B,C,<br>is (N x Font_Heigh |         |         |

### 2.10.3.2 Character Attribute (Default=XXXXXXXb)

| 7                           | 6                                                  | 5                                                            | 4                                                                                                            | 3                                            |                   | 2                      |                      | 1                            |          | 0    |

|-----------------------------|----------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------|------------------------|----------------------|------------------------------|----------|------|

| BG_R                        | BG_G                                               | BG_B                                                         | Blink                                                                                                        | FG_R                                         |                   | FG_G                   |                      | FG_B                         |          | FG_I |

| Bit 7-5<br>Bit 4<br>Bit 3-0 | Blink – Enable<br>FG_R/G/B/I or<br>0000b, then the | this Character dis<br>R_C2BP[3:0] – w<br>ere will be no fore | Color (Intensity=0<br>splay with blinking<br>/hen Character Da<br>ground, i.e. transp<br>h, these 4 bits act | feature. Refert<br>ata = 00h~BFh,<br>parent. | to sect<br>Foregr | ion 2.10.4<br>ound R/C | 4.10 for<br>3/B/Inte | detail blink<br>ensity Color | . If the |      |

### 2.10.3.3 Row Attribute (Default=XXXXXXXb)

| 7       | 6                                                                                                                                                                                    | 5       | 4       | 3       | 2       | 1   | 0   |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|-----|-----|--|--|

| RGAP_BG | RGAP[4]                                                                                                                                                                              | RGAP[3] | RGAP[2] | RGAP[1] | RGAP[0] | CHS | CWS |  |  |

| Bit 7   | Bit 7 RGAP_BG – Color Select of Row Gap. Set 1 for selecting the same color of background of current row character, 0 for selecting transparent color.                               |         |         |         |         |     |     |  |  |

| Bit 6-2 |                                                                                                                                                                                      |         |         |         |         |     |     |  |  |

| Bit 1   |                                                                                                                                                                                      |         |         |         |         |     |     |  |  |

| Bit 0   | Bit 0 CWS – Character Width Select. Set 1 for double width, 0 for single width. When set to 1, only the even numbered characters will be shown, odd numbered characters are skipped. |         |         |         |         |     |     |  |  |

#### 2.10.4 Configuration Register

### 2.10.4.1 Cfg\_00h – OSD Control Register (Default=00h => 18h)

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6       | 5      | 4        | 3        | 2         | 1       | 0       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|----------|----------|-----------|---------|---------|--|--|

| OSD_En                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit_Map | Bit2PP | Reserved | Reserved | Early_hDE | DCLK[1] | DCLK[0] |  |  |

| OSD_En         Bit_Map         Bit2PP         Reserved         Reserved         Early_hDE         DCLK[1]         DC           Bit 7         OSD_En – Enabling the OSD function. Set 1 for enabling, 0 for disabling OSD.         Bit 6         Bit 7         Bit 7         Bit 7         Bit 7         Bit 7         Bit 7         DCLK[1]         DC           Bit 6         Bit 7         Bit 7         Bit 7         Bit 7         Bit 7         DCLK[1]         DC           Bit 6         Bit 7         OSD_En – Enabling the OSD function. Set 1 for enabling, 0 for disabling OSD.         Bit 7         Bit 7 |         |        |          |          |           |         |         |  |  |

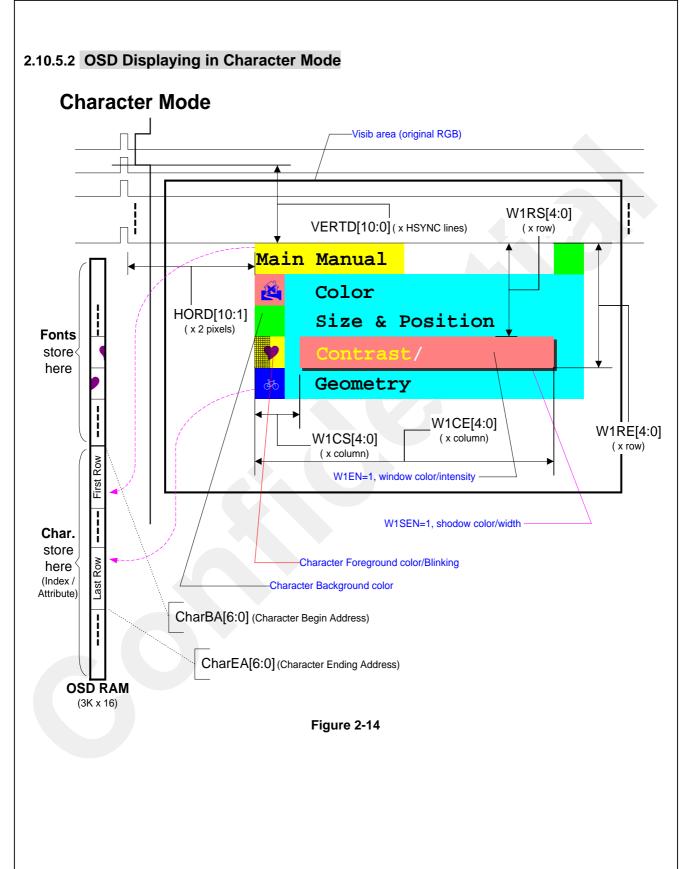

### 2.10.4.2 Cfg\_01h - Character Delay\_1 (Default=00h)

<sup>&</sup>lt;sup>1</sup> The "b" after value means Binary; "d" means Decimal; "h" means Hex-Decimal.

| 7        | 6                                                                                                                               | 5                   | 4                 | 3                     | 2                   | 1                | 0                |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-----------------------|---------------------|------------------|------------------|--|--|--|

| Reserved | VERTD[10]                                                                                                                       | VERTD[9]            | VERTD[8]          | Reserved              | HORD[10]            | HORD[9]          | HORD[8]          |  |  |  |

| Bit 7, 3 | Reserved. (R/W                                                                                                                  | keserved. (R/W)     |                   |                       |                     |                  |                  |  |  |  |

| Bit 6-4  | VERTD[10:8] -                                                                                                                   | Vertical Starting F | Position (Upper b | oits) of Character of | displaying. These b | its with Cfg_03h | , total 11 bits, |  |  |  |

|          | become 2048 steps, with an increment one pixel per step for each field.                                                         |                     |                   |                       |                     |                  |                  |  |  |  |

| Bit 2-0  | Bit 2-0 HORD[10:8] – Horizontal Starting Position (Upper bits) of Character displaying. These bits with Cfg_02h, total 11 bits, |                     |                   |                       |                     |                  |                  |  |  |  |

|          | become 2048 steps, with an increment one pixel per step.                                                                        |                     |                   |                       |                     |                  |                  |  |  |  |

### 2.10.4.3 Cfg\_02h - Character Delay\_2 (Default=10h)

| 7                                                                                                                                | 6       | 5       | 4       | 3       | 2       | 1       | 0       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| HORD[7]                                                                                                                          | HORD[6] | HORD[5] | HORD[4] | HORD[3] | HORD[2] | HORD[1] | HORD[0] |  |  |

| Bit 7-0 HORD[7:0] – Horizontal Starting Position (Lower bits) of Character displaying. This register with Cfg_01h<2:0>, total 11 |         |         |         |         |         |         |         |  |  |

bits, become 2048 steps, with an increment one pixel per step.

### 2.10.4.4 Cfg\_03h - Character Delay\_3 (Default=08h)

| _ | 7                                                                                                                               | 6        | 5        | 4        | 3        | 2        | 1        | 0        |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|--|--|

|   | VERTD[7]                                                                                                                        | VERTD[6] | VERTD[5] | VERTD[4] | VERTD[3] | VERTD[2] | VERTD[1] | VERTD[0] |  |  |

|   | Bit 7-0 VERTD[7:0] – Vertical Starting Position (Lower bits) of Character displaying. This register with Cfg_01h<6:4>, total 11 |          |          |          |          |          |          |          |  |  |

|   | bits become 2048 steps, with an increment one line per step for each field.                                                     |          |          |          |          |          |          |          |  |  |

### 2.10.4.5 Cfg\_04h - Character Font Size (Default=09h)

| <br>7       | 6                                                                                                                                          | 5               | 4        | 3        | 2        | 1        | 0        |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|----------|----------|----------|----------|--|--|--|--|

| Reserved    | Reserved                                                                                                                                   | Reserved        | FontH[1] | FontH[0] | Reserved | FontW[1] | FontW[0] |  |  |  |  |

| <br>Bit 7-5 | Reserved. (R/\                                                                                                                             | Reserved. (R/W) |          |          |          |          |          |  |  |  |  |

| Bit 4-3     | FontH [1:0] – Font Size (Height) Select. Set 00b for 16 lines, 01b for 18 lines, 10b for 24 lines, 11b for 32 lines. (default is 18 lines) |                 |          |          |          |          |          |  |  |  |  |

| Bit 2-0     | FontW [1:0] – Font Size (Width) Select. Set 00b for 10 dots, 01b for 12 dots, 10b for 14 dots, 11b for 16 dots. (default is 12 dots)       |                 |          |          |          |          |          |  |  |  |  |

## 2.10.4.6 Cfg\_05h - Char\_RAM Base Address (Default=50h)

|   | 7        | 6                                 | 5                                                     | 4                                  | 3                                        | 2                                                                                | 1                                     | 0                         |

|---|----------|-----------------------------------|-------------------------------------------------------|------------------------------------|------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|---------------------------|

|   | Reserved | CharBA[6]                         | CharBA[5]                                             | CharBA[4]                          | CharBA[3]                                | CharBA[2]                                                                        | CharBA[1]                             | CharBA[0]                 |

| _ | Bit 7    | Reserved. (R/V                    | V)                                                    |                                    |                                          |                                                                                  |                                       |                           |

|   | Bit 6-0  | (one Character<br>address will be | Row include Cha<br>RRRR-RRRX-XX<br>ading off Font nun | r_Index, Char_At<br>XX (The RRRR-I | ttr, Row_Attr; i.e. 3<br>RRR means the v | e 7 bits become 1<br>31 column maximu<br>alue of CharBA[6:<br>ngle RAM (this ver | um for each Row)<br>0]; the X-XXXX is | . The actual the nth Char |

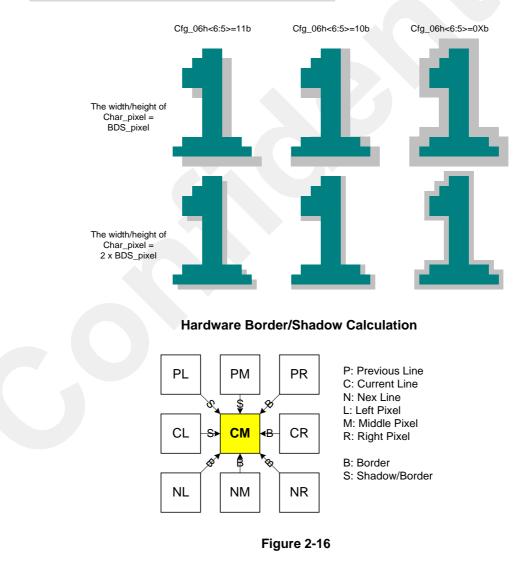

### 2.10.4.7 Cfg\_06h - Character Border / Shadow Control (Default=00h)

| 7       | 6                 | 5                                                                                                     | 4                  | 3                     | 2                    | 1                    | 0                  |  |  |  |

|---------|-------------------|-------------------------------------------------------------------------------------------------------|--------------------|-----------------------|----------------------|----------------------|--------------------|--|--|--|

| BDSEN   | CSHD              | ES_Only                                                                                               | Reserved           | BDSH[1]               | BDSH[0]              | BDSW[1]              | BDSW[0]            |  |  |  |

| Bit 7   | BDSEN - Cha       | BDSEN – Character Border/Shadow Enable. 1 for enabling Border or Shadow (depends on CSHD setting, the |                    |                       |                      |                      |                    |  |  |  |

|         | Cfg_06h<6>).      |                                                                                                       |                    |                       |                      |                      |                    |  |  |  |

| Bit 6   |                   |                                                                                                       |                    | Cfg_06h<7>) is 0,     |                      | hadow displaying     | for Character; it  |  |  |  |

|         | ,                 |                                                                                                       | 0                  | Shadow, 0 for sele    | 0                    |                      |                    |  |  |  |

| Bit 5   |                   |                                                                                                       |                    | displayed foregrou    |                      |                      | est light source), |  |  |  |

|         | if set to 1; else | the shadow also                                                                                       | exist on the both  | east & south side     | of displayed foreg   | ground dot.          |                    |  |  |  |

| Bit 4   | Reserved.         |                                                                                                       |                    |                       |                      |                      |                    |  |  |  |

| Bit 3-2 | BDSH [1:0] – 0    | Character Border/                                                                                     | Shadow Height. S   | Set 00b for 1 line, ( | 01b for 2 lines, 10  | b for 3 lines, 11b f | or 4 lines. The    |  |  |  |

|         | BDSH[1:0] valu    | ue must <= DCLk                                                                                       | [1:0]; Only 00b (o | ne line height) ava   | ailable in current v | ersion.              |                    |  |  |  |

| Bit 1-0 | BDSW [1:0] - 0    | Character Border                                                                                      | Shadow Width. S    | set 00b for 1 pixel,  | 01b for 2 pixels, 1  | 10b for 3 pixels, 11 | 1b for 4 pixels.   |  |  |  |

|         | The BDSW[1:0      | )] value must <= (                                                                                    | CHD[2:0]; Only 00  | b (one pixel width)   | ) available in curre | ent version.         |                    |  |  |  |

|         |                   |                                                                                                       |                    |                       |                      |                      |                    |  |  |  |

|         |                   |                                                                                                       |                    |                       |                      |                      |                    |  |  |  |

### 2.10.4.8 Cfg\_07h – Character Border / Shadow Color & Output Delay (Default=00h)

| 7                              | 6                                                                     | 5                                                                          | Δ                                                                                                       | 3                                                                                    | 2                                                                          | 1                                      | 0                 |

|--------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|-------------------|

| BDS_R                          | BDS G                                                                 | BDS B                                                                      | BDS Gray                                                                                                | Reserved                                                                             | Reserved                                                                   | Reserved                               | Reserved          |

| Bit 7-4                        | BDS_R/G/B/Gr<br>levels, else, sel                                     | ay – Character B<br>lect half the R/G/                                     | Border (or Shadow)<br>B value (Intensity=<br>half Character Bac                                         | ) R/G/B color and<br>⊧0) of OSD LUT c                                                | Gray level select.                                                         | When BDS_Gray                          | y=1, select 8 gra |

| 2.10.4.9 Cfg                   | _08h – Cha                                                            | racter Heig                                                                | ght Control                                                                                             | (Default=2                                                                           | 0h)                                                                        |                                        |                   |

| 7                              | 6                                                                     | 5                                                                          | 4                                                                                                       | 3                                                                                    | 2                                                                          | 1                                      | 0                 |

| CHD[2]                         | CHD[1]                                                                | CHD[0]                                                                     | Reserved                                                                                                | Reserved                                                                             | Reserved                                                                   | Reserved                               | Reserved          |

| Bit 7-0                        |                                                                       | aracter height du                                                          | plicate, select the                                                                                     | duplicate number                                                                     | rs of each lines (16                                                       | 3/18/24/32). The (                     | CHD[2:0] must >   |

| Bit 4-0                        | 1.<br>Reserved.                                                       |                                                                            |                                                                                                         |                                                                                      |                                                                            |                                        |                   |

| .10.4.10                       | Cfg_09h -                                                             | - Blinking                                                                 | Control (De                                                                                             | fault=0Ah)                                                                           |                                                                            |                                        |                   |

| 7                              | 6                                                                     | 5                                                                          | 4                                                                                                       | 3                                                                                    | 2                                                                          | 1                                      | 0                 |

| Reserved                       | Reserved                                                              | Reserved                                                                   | Reserved                                                                                                | BCLK[1]                                                                              | BCLK[0]                                                                    | Duty[1]                                | Duty[0]           |

| Bit 1-0                        | Duty[1:0] – For<br>00b for Global<br>01b for 25% Ba<br>10b for 50% Ba |                                                                            | nking duty cycle, S<br>Background, 100<br>OSD.<br>OSD.                                                  |                                                                                      |                                                                            |                                        |                   |

| .10.4.11                       | Cfg_0Ah                                                               | – Bit_Map                                                                  | Window Siz                                                                                              | ze: Width/H                                                                          | leight Uppe                                                                | r Bits (Defa                           | ault=00h)         |

| 7                              | 6                                                                     | 5                                                                          | 4                                                                                                       | 3                                                                                    | 2                                                                          | 1                                      | 0                 |

| Reserved                       | BMH[10]                                                               | BMH[9]                                                                     | BMH[8]                                                                                                  | Reserved                                                                             | BMW[10]                                                                    | BMW[9]                                 | BMW[8]            |

| Bit 7, 3<br>Bit 6-4<br>Bit 2-0 | User must be c<br>BMW[10:8] – B                                       | it Map Window H<br>careful of the OSI<br>it Map Window V                   | eight Upper bits (c<br>D RAM size limitati<br>Vidth Upper bits (o<br>D RAM size limitati                | on.<br>nly available in B                                                            | ,                                                                          | 0-                                     | _                 |

| .10.4.12                       | Cfg_0Bh                                                               | – Bit_Map                                                                  | Window Siz                                                                                              | ze: Width (I                                                                         | Default=80h                                                                | 1)                                     |                   |

| 7                              | 6                                                                     | 5                                                                          | 4                                                                                                       | 3                                                                                    | 2                                                                          | 1                                      | 0                 |

| BMW[7]                         | BMW[6]                                                                | BMW[5]                                                                     | BMW[4]                                                                                                  | BMW[3]                                                                               | BMW[2]                                                                     | BMW[1]                                 | BMW[0]            |

| Bit 7-0                        | BMW[7:0] – Bit<br>Cfg_0Ah<2:0><br>Bit2PP (Cfg_00<br>each step is 8 o  | Map Window Wi<br>and become 11 I<br>Dh<5>) setting. W<br>dots. User must b | idth Lower bits (on<br>bits, i.e., 2047 step<br>/hen Bit2PP=0 (i.e<br>be careful of the O<br>Window Siz | ly available in Bit<br>os (value 000h is<br>., 4 bits/pixel), ea<br>SD RAM size limi | _Map mode This r<br>not valid), each st<br>ich step is 4 dots.<br>itation. | ep is 4 or 8 dots o<br>When Bit2PP=1 ( | depends on        |

|                                |                                                                       |                                                                            |                                                                                                         |                                                                                      |                                                                            |                                        |                   |

| 7                              | 6                                                                     | 5                                                                          | 4                                                                                                       | 3                                                                                    | 2                                                                          | 1                                      | 0                 |

| BMH[7]                         | BMH[6]                                                                | BMH[5]                                                                     | BMH[4]                                                                                                  | BMH[3]                                                                               | BMH[2]                                                                     | BMH[1]                                 | BMH[0]            |

| Bit 7-0                        | Cfg_0Ah<6:4>                                                          | and become 11 I                                                            | ight Lower bits (or<br>bits, i.e. 2048 heig<br>D RAM size limitati                                      | ht step: all 0 for 2                                                                 |                                                                            |                                        |                   |

### 2.10.4.14 Cfg\_0Dh – Bit\_Map Dot Enlarge (Default=11h)

| -                                                                                                                              | - <b>J</b>                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                      | J                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7                                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                                                                                                                                                                                                                                    | 4                                                                                                                                                                                                                                                                                                               | 3                                                                                                                                                                                                                                            | 2                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                             | 0                                                                                                                                        |

| BMBigH[3]                                                                                                                      | BMBigH[2]                                                                                                                                                                                                                                                                                                                                                                    | BMBigH[1]                                                                                                                                                                                                                                                                                            | BMBigH[0]                                                                                                                                                                                                                                                                                                       | BMBigW[3]                                                                                                                                                                                                                                    | BMBigW[2]                                                                                                                                                                                                                                       | BMBigW[1]                                                                                                                                                                                                                                                     | BMBigW[0]                                                                                                                                |

| Bit 7-4                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                 | Set 0000b for 1 lin                                                                                                                                                                                                                                           | e per dot, 0001b                                                                                                                         |

| Bit 3-0                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                      | nes,, 1111b for<br>Horizontal Enlard                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                 | e). Set 0000b for 1                                                                                                                                                                                                                                           | pixel per dot                                                                                                                            |

| Diroo                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                 | 1111b for 30 pixe                                                                                                                                                                                                                                             |                                                                                                                                          |

|                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                             |                                                                                                                                          |